## **High Efficiency Boost DC/DC Convertor**

## **General Description**

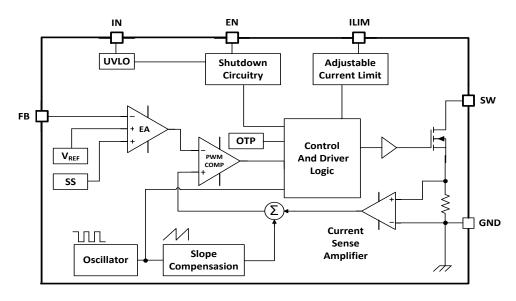

LP6224 is an asynchronous boost chip controlled by peak current mode, with a fixed switching frequency of 900Khz. The compensation network is integrated internally and no external components are needed to compensate. The integrated soft start circuit can effectively control the inrush current during startup and prevent the battery or external power supply voltage from being pulled down. In addition, the switching current limit can be programmed through external resistors to respond to different power supply system requirements.

LP6224 can automatically enter PFM mode under light load to improving the conversion efficiency. With the load current increasing, the chip enters PWM mode, in which the frequency band of output ripple is relatively fixed and the conversion efficiency will be highly. The LP6224 integrates under-voltage, overcurrent, over-temperature and other protection functions.

The LP6224 provides the smaller SOT23-6 package.

### **Order Information**

### **Applications**

- Battery products

- ♦ Host Products

- ♦ Panel

### **Features**

- 2.5V to 15V Input Voltage

- ◆ Up to 92% efficiency

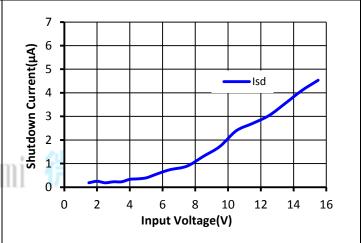

- ♦ Shut-down current:<1uA @ V<sub>IN</sub>=5V

- Integrated 80mΩ Power MOSFET

- Adjustable Output voltage Up to 18V

- Internal Compensation, Soft-start

- 900KHz fixed frequency switching

- Intenal Switching Current Limit (Current Limit Supports externally adjustable)

- ◆ Available in SOT23-6 Package

- ◆ RoHS Compliant and 100% Lead (Pb)-Free

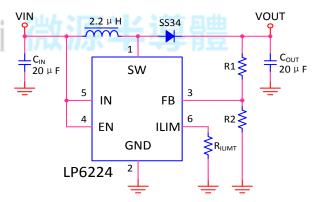

## **Typical Application Circuit**

## **Marking Information**

| Device                                                   | Marking      | Package  | Shipping |  |

|----------------------------------------------------------|--------------|----------|----------|--|

| LP6224B6F                                                | LPS<br>5FYWX | SOT23-6L | 3K/REEL  |  |

| Marking indication:                                      |              |          |          |  |

| Y:Production year W:Production period X:Production batch |              |          |          |  |

LP6224-02

Page 2 of 9

# **Functional Pin Description**

| Package Type | Pin Configurations                             |  |  |

|--------------|------------------------------------------------|--|--|

| SOT23-6      | SW 1 6 ILIM  GND 2 5 IN  FB 3 4 EN  (Top View) |  |  |

# **Pin Description**

| Pin | Name                                                                   | Description                                                                                       |

|-----|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 1   | SW                                                                     | Power Switch Output. SW is the drain of the internal MOSFET switch. Connect the                   |

|     |                                                                        | powe <mark>r</mark> inductor and outp <mark>ut</mark> rectifier to SW.                            |

| 2   | GND                                                                    | Ground pin.                                                                                       |

| 3   | FB                                                                     | Output voltage feedback pin. Connect to an external resistive voltage divider from the            |

|     |                                                                        | output to FB to set the output voltage.                                                           |

| 4   | EN                                                                     | Regulator ON/OFF Control Input. A logic high input(V <sub>EN</sub> >1.4V) turns on the converter. |

| 4   |                                                                        | A logic low input( $V_{EN}$ <0.4V) puts the LP6224 into low current shutdown mode.                |

| 5   | 5 IN Power Supply pin. Place a bypass capacitor as locally as possible |                                                                                                   |

| 6   | ILIM                                                                   | Program Peak inductance current pin. If no connected or connected to GND, The                     |

| 0   |                                                                        | device will select internal current limit.                                                        |

LP6224-02 Sep.-2021 Email: marketing@lowpowersemi.com www.lowpowersemi.com

### **Function Block Diagram**

# **Absolute Maximum Ratings** Note 1

| <b></b>   | Input to GND                                           |

|-----------|--------------------------------------------------------|

| <b></b>   | EN to GND                                              |

| <b>\$</b> | SW Voltage to GND0.3V to 25V                           |

| <b></b>   | FB to GND                                              |

| <b></b>   | Other Pin Voltage to GND                               |

| <b></b>   | Maximum Junction Temperature 150°C                     |

| <b></b>   | Maximum Soldering Temperature (at leads, 10 sec) 260°C |

**Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Thermal Information**

| $\diamondsuit$ | $\label{eq:maximum Power Dissipation (PD,TA=25°C)} 0.45W$ |

|----------------|-----------------------------------------------------------|

| <b></b>        | Thermal Resistance (J <sub>A</sub> ) 250°C/W              |

| ES             | SD Susceptibility                                         |

# ♦ HBM(Human Body Mode) ------ 2KV

♦ MM(Machine Mode) ------ 200V

## **Recommended Operating Conditions**

www.lowpowersemi.com

### **Electrical Characteristics**

$(T_A = 25 ^{\circ}\text{C}, V_{\text{IN}} = 3.3 \text{V}, \ V_{\text{OUT}} = 5 \text{V}, \ C_{\text{IN}} = 20 \text{uF}, \ C_{\text{OUT}} = 20 \text{uF}, \ L = 2.2 \text{uH}, \ R_1 = 110 \text{K}, \ R_2 = 15 \text{K})$

| Parameter                       | Symbol              | Condition            | Min   | Тур. | Max   | Units |

|---------------------------------|---------------------|----------------------|-------|------|-------|-------|

| Input Supply Range              | V <sub>CC</sub>     |                      | 2.5   |      | 15    | V     |

| Under Voltage Lockout           | V <sub>UVLO</sub>   |                      |       | 2.3  |       | V     |

| UVLO Hysteresis                 |                     |                      |       | 160  |       | mV    |

| Output Voltage Range            | V <sub>OUT</sub>    |                      | 2.5   |      | 18    | V     |

| Quiescent Current               |                     | VFB=0.7V, No Switch  |       | 240  |       | μΑ    |

| Quiescent Current               | IQ                  | VFB=0.5V, Switch     |       | 1.2  |       | mA    |

| Shutdown Supply Current         | I <sub>SD</sub>     | V <sub>EN</sub> =0V  |       |      | 0.1   | uA    |

| Switching Frequency             | Fosc                |                      |       | 900  |       | KHz   |

| Maximum Duty Cycle              | D <sub>UTY</sub>    |                      |       |      | 85    | %     |

| Reference Voltage               | $V_{REF}$           |                      | 0.588 | 0.6  | 0.612 | V     |

| EN Input Low Voltage            | V <sub>EN_OFF</sub> |                      |       |      | 0.4   | V     |

| EN Input High Voltage           | V <sub>EN_ON</sub>  |                      | 1.4   |      |       | V     |

| Over Current Protection         | LowD                | No Connection RILIMT | 道     | 2500 |       | mA    |

| Over Current Protection         | loce                | RILIMT=10~400K       | 500   | 52   | 3400  | mA    |

| Over Temperature Protection     | OTP                 |                      |       | 150  |       | °C    |

| Overcurrent recovery hysteresis |                     |                      |       |      | 20    | °C    |

| Low-side On Resistance          | R <sub>DS(ON)</sub> |                      |       | 80   |       | mΩ    |

LP6224-02 Sep.-2021 Email: marketing@lowpowersemi.com www.lowpowersemi.com

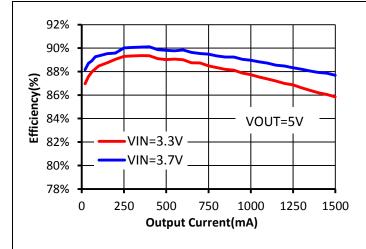

## **Typical Operating Characteristics**

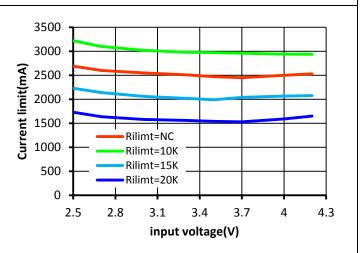

(C<sub>IN</sub>=20uF, C<sub>OUT</sub>=20uF, T<sub>A</sub>=25℃, unless otherwise noted)

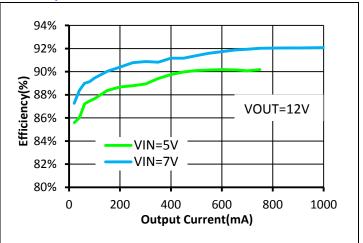

Figure 1. Output efficiency with load

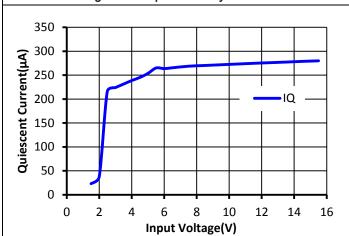

Figure 3.Input Voltage vs Quiescent Current

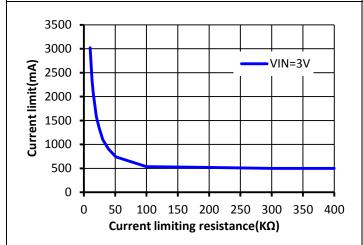

Figure 5. Current Limiting Resistance vs Maximum Current

Limiting

Figure 2. Output efficiency with load

Figure 4. Input Voltage vs Shutdown Current

Figure 6. Input Voltage vs Maximum Current Limit@

Different Current Limiting Resistors

LP6224-02

Sep.-2021

Email: marketing@lowpowersemi.com

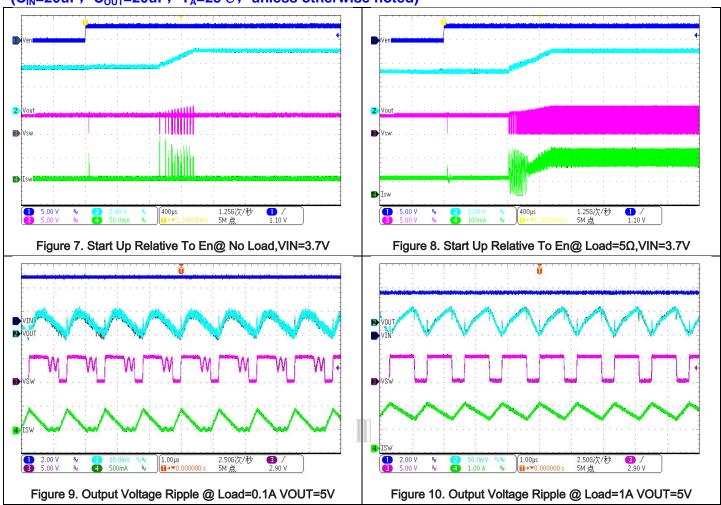

## **Application Waveform**

( $C_{\text{IN}}$ =20uF,  $C_{\text{OUT}}$ =20uF,  $T_{\text{A}}$ =25 $^{\circ}$ C, unless otherwise noted)

### **Operation Information**

LP6224 adopts fixed frequency 900 KHz, peak current mode control structure. The integrated harmonic compensation circuit can make a compensate signal on the current signal, which prevent the device from the sub-harmonic oscillation when the duty ratio is more than 50%, The output voltage and switch current limit can be programmed by external resistance,

### **Setting the Output Voltage**

The output voltage is set by an external resistor divider. The internal reference  $V_{\text{REF}}$  is 0.6V (typical).For the best accuracy and stability, The R2 resistor should be kept small than  $200k\,\Omega$ , Because a lower value increases the immunity against noise injection. The output voltage is given by

$$V_{OUT} = (R1/R2 + 1) \times V_{REF}$$

# Current Limitation PSemi

In order to prevent thermal destabilization or thermal run away in the low-side Power MOSFET, The chip designed a cycle-by-cycle current limit circuit. If the output current becomes very heavy, and the inductor peak current hit the current limit, the chip will turn off the Power MOSFET, In this case the output voltage will further decrease.

#### **Setting Peak Current Limit**

The current limit of inductance is set by external resistance programming between ILIM and GND .The relationship between the current limit and the resistors is Show in Figure 5&6. In addition, The device selects the internal switch current limit while the ILIM pin is no connected or connected to GND.

#### **Thermal Shutdown**

A thermal shutdown is implemented to prevent damage due to the excessive heat and power dissipation. Typically, the thermal shutdown occurs at the junction temperature exceeding 150°C. When the thermal shutdown is triggered, the device stops switching. while the junction temperature falls below 130°C, the device will restart to work.

#### **Diode Selection**

Schottky diodes with fast recovery times and low forward guide voltages are recommended to select, To ensure that the average peak current rating of the continuous tube exceeds the average output current and peak inductance current, it also can pass through a large peak pulse current. In addition, the reverse breakdown voltage of the diode must exceed the output voltage

### **Input and Output Capacitor Selection**

For better input bypassing, low-ESR ceramic capacitors are recommended for performance. A 20uF input capacitor is sufficient for most applications. For a lower output power requirement application, this value can be decreased.

#### **Shut Down**

When the input voltage is below the V<sub>UVLO</sub> threshold or the EN pin is pulled low, the chip is in shutdown mode and all the functions are disabled.

#### **Soft Start**

The soft start feature helps the converter gradually reach a stable output voltage, thus reducing the uprush output voltage and inrush current at start-up. When a voltage is applied to the input, the input is charged to the output capacitance through an inductor and a high-side rectifier diode. After reaching V<sub>UVLO</sub> threshold, an internal soft-start control circuit ramps the reference voltage to 0.6V within 2ms.After the output voltage reaches the target value, soft start ends.

#### **Inductor Selection**

For a better efficiency in high switching frequency

LP6224-02

Sep.-2021

Email: marketing@lowpowersemi.com

converter, the inductor selection has to use a proper core material such as ferrite core to reduce the core loss and choose low ESR wire to reduce copper loss. The most important point is to prevent the core saturated when handling the maximum peak current. Using a shielded inductor can minimize radiated noise in sensitive applications. The maximum peak inductor current is the maximum input current plus the half of inductor ripple current. The calculated peak current has to be smaller than the current limitation in the electrical characteristics. A typical setting of the inductor ripple current is 20% to 40% of the maximum input current. If the selection is 40%, the maximum peak inductor current is

$$\begin{split} I_{PEAK} &= I_{IN(MAX)} + \frac{1}{2}I_{RIPPLR} \\ &= 1.2 \times I_{IN(MAX)} \\ &= 1.2 \times \left[ \frac{I_{OUT(MAX)} \times V_{OUT}}{\eta \times V_{IN(MAX)}} \right] \end{split}$$

The minimum inductance value is derived from the following equation:

$$L = \frac{\eta \times V_{IN(MAX)}^{2} \times \left[V_{OUT} - V_{IN(MIN)}\right]}{0.4 \times I_{OUT(MAX)} \times V_{OUT}^{2} \times f_{OSC}}$$

Depending on the application, the recommended inductor value is between 2.2uH to 10uH.

### **Output Capacitor Selection**

For lower output voltage ripple, low-ESR ceramic capacitors recommended. The tantalum are capacitors can be used as well, but the ESR is bigger than ceramic capacitor. The output voltage ripple consists of two components: one is the pulsating output ripple current flows through the ESR, and the other is the capacitive ripple caused by charging and discharging.

$$\begin{split} V_{RIPPLE} &= V_{RIPPLE_{ESR}} + V_{RIPPLE_{C}} \\ &\cong I_{PEAK} \times R_{ESR} + \frac{I_{PEAK}}{C_{OUT}} \Big( \frac{V_{OUT} - V_{IN}}{V_{OUT} \times f_{OSC}} \Big) \end{split}$$

### **Layout Guideline**

For high frequency switching power supplies, the PCB layout is important step in system application design. In order to let IC achieve good regulation, high efficiency and stability, it is strongly recommended the power components should be placed as close as possible. The set circuit races should be wide and short. The feedback pin and then works of feedback and compensation should keep away from the power loops, and be shielded with a ground trace or plane to prevent noise coupling.

LP6224-02

Sep.-2021

Email: marketing@lowpowersemi.com

www.lowpowersemi.com

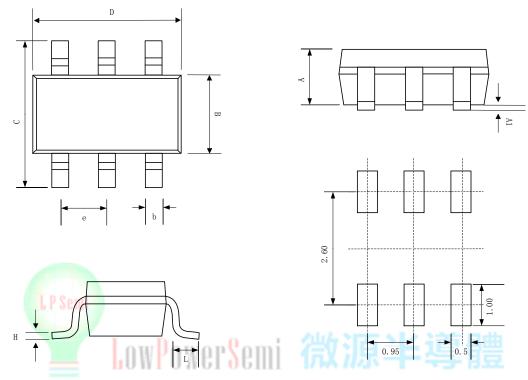

# **Packaging Information**

### **SOT23-6**

Recommended Land Pattern

|        | MILLIMETER |       |       |  |  |  |

|--------|------------|-------|-------|--|--|--|

| SYMBOL |            |       |       |  |  |  |

|        | MIN        | NOM   | MAX   |  |  |  |

| A      | 0.889      | 1.100 | 1.295 |  |  |  |

| A1     | 0.000      | 0.050 | 0.152 |  |  |  |

| В      | 1.397      | 1.600 | 1.803 |  |  |  |

| b      | 0.28       | 0.35  | 0.559 |  |  |  |

| С      | 2.591      | 2.800 | 3.000 |  |  |  |

| D      | 2.692      | 2.920 | 3.120 |  |  |  |

| е      | 0.95BSC    |       |       |  |  |  |

| Н      | 0.080      | 0.152 | 0.254 |  |  |  |

| L      | 0.300      | 0.450 | 0.610 |  |  |  |

LP6224-02 Se

Sep.-2021

Email: marketing@lowpowersemi.com