# LP6280S Dual Output Power Supply for LCD Bias

### **Features**

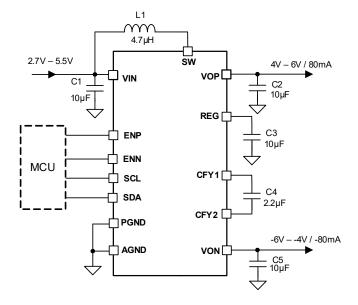

- Input voltage range: 2.7V to 5.5V

- Programmable output voltages

- VOP output voltage: 4V to 6V with 0.1V per step

- VON output voltage: -6V to -4V with 0.1V per step

- Optimized for 80mA operation

- 88% efficiency at VIN=4.4V, VOP/VON = +/-5.4V, 80mA output per channel

- I2C Interface

- Flexible Output Voltage Programming

- Programmable Active Output Discharge

- Protections

- Input under-voltage lockout (UVLO)

- Boost cycle-by-cycle current-limit protection

- Output current limit and short circuit protection

- Thermal shutdown protection

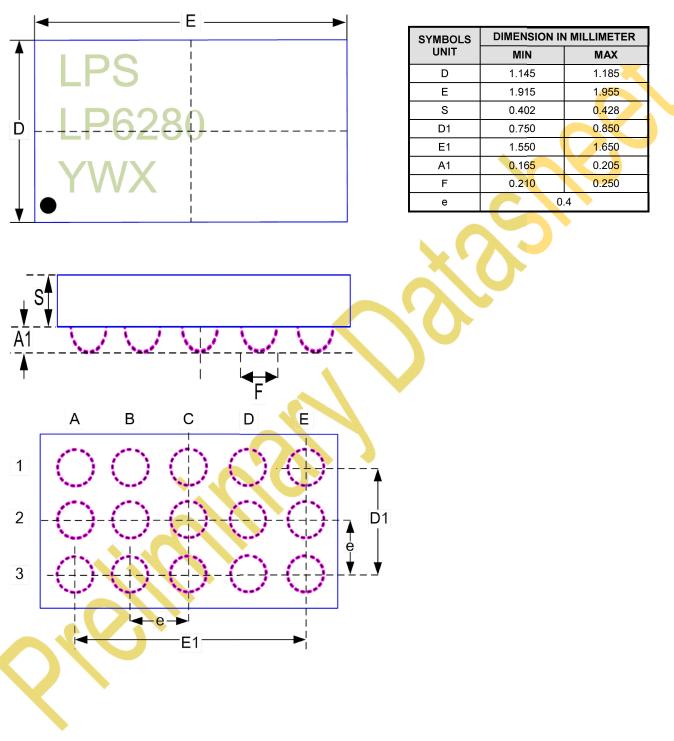

- Packaging

- WLCSP 15 balls (1.19mm x 1.96mm)

- RoHS Compliant and Halogen Free

- 100% Lead (Pb) Free

### **Order Information**

LP6280S

- F: Pb-Free Package Type HV: WLCSP-15

### **General Description**

The LP6280S is designed to supply positive/negative driven applications. The device uses a single inductor scheme to provide both output currents. The integrated synchronous Boost converter provides a regulated voltage for a LDO and a charge pump. The LDO provides a regulated and programmable positive bias VOP and the

provides charge pump а regulated and programmable negative bias VON. The device offers low noise, small solution size and high efficiency. The other feature includes under-voltage lockout (UVLO), internal soft-start, Boost cycle-by-cycle current limit and output over load and short circuit protection as well as thermal shutdown. The LP6280S is available in a space saving WLCSP 15-ball (0.4mm pitch) package.

## **Applications**

- Small-, Medium-Size Bipolar LCD Displays

- Smartphone, Tablet

- Camera, GPS

- Home Automation, Point-of-Sales

- Wearables (Smart Watch, Activity Tracker)

- General Split-Rail Power Supply for

- Differential Audio, Headphone Amplifier

- Instrumentation, Operational

- Amplifier, Comparator

- DAC/ADC

## **Typical Application Circuit**

## **Device Information**

| Part Number                               | Top Marking           | Package  | Moisture Sensitivity Level | Shipping |

|-------------------------------------------|-----------------------|----------|----------------------------|----------|

| LP6280S                                   | LPS<br>LP6280S<br>YWX | WLCSP-15 | MSL1                       | 3K/REEL  |

| Marking indication:<br>Y: Year Code. W: V | Week Code. X: Batch N | umbers.  |                            |          |

|                                           |                       |          |                            |          |

## Pin Diagram

15-ball WLCSP (Top View)

## **Pin Description**

|        | -     |                                                                                               |  |  |  |  |

|--------|-------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| Pin    | Name  | Description                                                                                   |  |  |  |  |

| A1     | ENN   | Enable input for VON rail.                                                                    |  |  |  |  |

| A2     | VON   | Negative voltage output. Decouple this pin to PGND with a $10\mu F$ or higher ceramic         |  |  |  |  |

| AZ     | VON   | capacitor as close to this pin as possible.                                                   |  |  |  |  |

| A3     | CFLY2 | Negative input for the external flying capacitor. Connect a terminal of a $2.2\mu F$          |  |  |  |  |

| AS     | GFLTZ | ceramic capacitor close to this pin.                                                          |  |  |  |  |

| B1     | ENP   | Enable input for VOP rail.                                                                    |  |  |  |  |

| B2     | SCL   | I2C interface clock signal.                                                                   |  |  |  |  |

| B3, E1 | PGND  | Power ground.                                                                                 |  |  |  |  |

| C1     | VIN   | Supply voltage input. Connect at least 10µF ceramic capacitor from this pin to                |  |  |  |  |

| CI     | VIIN  | PGND.                                                                                         |  |  |  |  |

| C2     | SDA   | I2C interface data signal.                                                                    |  |  |  |  |

| C3     | CFLY1 | Positive input for the external flying capacitor. Connect the other terminal of a $2.2 \mu F$ |  |  |  |  |

| 03     | CFLTI | ceramic capacitor close to this pin.                                                          |  |  |  |  |

| D1     | SW    | Switching node output. Connect a terminal of an external inductor to this switching           |  |  |  |  |

|        | 500   | node. Short and wide trace is required for SW connection.                                     |  |  |  |  |

| D2     | AGND  | Analog ground. Control circuitry returns current to this pin.                                 |  |  |  |  |

| D3, E2 | REG   | Boost converter regulated output. Decouple this pin to PGND with a $10\mu F$ or higher        |  |  |  |  |

| □3, ⊏2 | REG   | ceramic capacitor as close to this pin as possible.                                           |  |  |  |  |

| E3     | VOP   | Positive voltage output. Decouple this pin to PGND with a $10\mu F$ or higher ceramic         |  |  |  |  |

| ES     | VUF   | capacitor as close to this pin as possible.                                                   |  |  |  |  |

|        |       |                                                                                               |  |  |  |  |

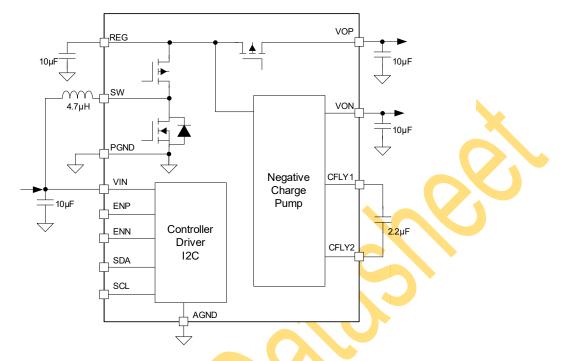

### **Functional Block Diagram**

### Absolute Maximum Ratings (1)

| • | VIN, SW, REG, VOP, VCFLY1, SDA, SCL Voltage to GND |               |

|---|----------------------------------------------------|---------------|

| • | VENN, VENP Voltage to GND                          |               |

| • | VON, VCFLY2 Voltage to GND                         |               |

| • | Maximum Junction Temperature (TJ)                  | 150°C         |

| • | Storage Temperature Range                          | 40°C to 150°C |

| • | Maximum Soldering Temperature (at leads, 10 sec)   | 260°C         |

Note: (1) Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD Susceptibility**

| • | HBM(Human Body Mo | odel) | 2KV  |

|---|-------------------|-------|------|

| ٠ | MM(Machine Model) |       | 200V |

## **Recommended Operating Conditions**

| PARAMETER                        |                                                        | MIN  | NOM  | MAX   | UNIT |

|----------------------------------|--------------------------------------------------------|------|------|-------|------|

| VIN                              | Input Voltage                                          | 2.7  |      | 5.5   | V    |

| I <sub>VOP</sub>                 | Positive Output Current                                |      |      | 80(1) | mA   |

| I <sub>VON</sub>                 | Negative Output Current                                |      |      | 80(1) | mA   |

| V <sub>VOP</sub>                 | Positive Output Voltage                                | 4.0  | 5.5  | 6.0   | V    |

| V <sub>VON</sub>                 | Negative Output Voltage                                | -6.0 | -5.5 | -4.0  | V    |

| TJ                               | Operating Junction Temperature Range (T <sub>J</sub> ) | -40  |      | 125   | °C   |

| T <sub>A</sub>                   | Ambient Temperature Range                              | -40  |      | 85    | °C   |

| θ <sub>JA</sub>                  | Thermal Resistance                                     |      | 85   |       | °C/W |

| θ <sub>JC</sub>                  | Thermal Resistance                                     |      | 1    |       | °C/W |

| L                                | Boost Inductance <sup>(2)</sup>                        | 3.76 | 4.7  | 5.64  | μH   |

| C <sub>IN</sub>                  | Input Capacitance <sup>(2) (3)</sup>                   | 4    | 10   | 30    | μF   |

| C <sub>REG</sub>                 | Boost Output Capacitance <sup>(2) (3)</sup>            | 4    | 10   | 30    | μF   |

| C <sub>FLY</sub>                 | Flying capacitance <sup>(2) (3)</sup>                  | 0.9  | 2.2  | 2.64  | μF   |

| $C_{\text{VOP},}C_{\text{VON},}$ | Output Capacitance <sup>(2) (3)</sup>                  | 4    | 10   | 30    | μF   |

Note:

- (1) The transient output current is allowed up to 150mA with higher output voltage drop.

- (2) The values recommended in the table are effective inductance and capacitance.

- (3) X7R, 0603 size and 10V (or 16V) voltage rating capacitors are recommended.

### **Electrical Characteristics**

(The specifications are at  $T_A=25^{\circ}$ C,  $V_{IN} = 3.7$ V,  $V_{OP} = 5$ V,  $V_{ON} = -5$ V, unless otherwise noted.)

| Symbol Parameter              |                              | Condition                                         | Min  | Тур  | Max  | Units                                   |  |

|-------------------------------|------------------------------|---------------------------------------------------|------|------|------|-----------------------------------------|--|

| INPUT VOL                     | TAGE AND CURRENT             |                                                   |      |      |      |                                         |  |

| VIN                           | Input Voltage Range          |                                                   | 2.7  |      | 5.5  | V                                       |  |

|                               |                              | VENN and VENP are tied                            |      |      |      |                                         |  |

| lq                            | Input Supply Current         | to AGND                                           |      |      | 1    | μA                                      |  |

|                               |                              |                                                   |      |      |      |                                         |  |

| lα                            | Input Supply Current         |                                                   |      | 1    |      | mA                                      |  |

|                               | Under Voltage                |                                                   |      |      |      |                                         |  |

| $V_{\text{IN}_{\text{UVLO}}}$ | Lockout of V <sub>IN</sub>   | V <sub>IN</sub> Rising                            | 2.2  | 2.4  | 2.65 | V                                       |  |

| VIN_UVLO_HYS                  | V <sub>UVLO</sub> Hysteresis | V <sub>IN</sub> Falling                           |      | 300  |      | mV                                      |  |

| SWITCHIN                      | G BOOST CONVERTER            |                                                   |      |      |      |                                         |  |

|                               |                              | The old DS is OSC                                 |      |      |      |                                         |  |

| $F_{SW}$                      | Switching Frequency          | frequency                                         | 0.96 | 1.2  | 1.44 | MHz                                     |  |

| I <sub>LIM</sub>              | Switch Current Limit         |                                                   |      | 1.5  |      | Α                                       |  |

| D <sub>MAX</sub>              | Maximum Duty Cycle           |                                                   |      | 90   |      | %                                       |  |

| R <sub>DSON_HS</sub>          | High-side MOSFET             |                                                   |      |      |      |                                         |  |

|                               | On-resistance                |                                                   |      | 0.3  |      | Ω                                       |  |

| R <sub>DSON_LS</sub>          | Low-side MOSFET              |                                                   |      | 0.3  |      | Ω                                       |  |

| TOSON_LS                      | On-resistance                |                                                   |      | 0.5  |      | 52                                      |  |

| POSITIVE O                    | UTPUT VOLTAGE LDO            |                                                   |      |      |      |                                         |  |

| V <sub>OP</sub>               | Positive Output Voltage      | 21 steps, each step                               | 4.0  |      | 6.0  | V                                       |  |

| ♥ OP                          | Range                        | 100mV                                             | 4.0  |      | 0.0  | •                                       |  |

| V <sub>OP_ACC</sub>           | Positive Output Voltage      |                                                   | -1.0 |      | +1.0 | %                                       |  |

|                               | Accuracy                     |                                                   |      |      |      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |  |

| V <sub>DROP</sub>             | Dropout voltage              | V <sub>OP</sub> =5V, I <sub>OP</sub> =80mA        |      | 250  |      | mV                                      |  |

|                               | Line Regulation              | V <sub>IN</sub> =2.5V~4.2V, I <sub>OP</sub> =80mA |      | 1    |      | %                                       |  |

|                               | Load Regulation              | I <sub>OP</sub> =10mA to 80mA,                    |      | 1    |      | %                                       |  |

|                               |                              | I <sub>OP</sub> =5.4V                             |      |      |      |                                         |  |

|                               | VOP Discharge Resistance     | V <sub>OP</sub> = 5.4V                            |      | 40   |      | Ω                                       |  |

| V <sub>ENP(H)</sub>           |                              |                                                   | 1.2  |      |      | V                                       |  |

| V <sub>ENP(L)</sub>           |                              |                                                   |      |      | 0.4  | V                                       |  |

|                               | ENP Sink Current             | V <sub>ENP</sub> =2V                              |      | 10   |      | μA                                      |  |

| I <sub>LIM</sub>              | Output Current Limit         |                                                   |      | 0.3  |      | Α                                       |  |

| ISCP                          | Short Circuit Current        | $V_{OP}$ < 40% of setting                         |      | 0.15 |      | А                                       |  |

## **Electrical Characteristics (Continued)**

(The specifications are at T<sub>A</sub>=25°C,  $V_{IN}$  = 3.7V,  $V_{OP}$  = 5V,  $V_{ON}$  = -5V, unless otherwise noted.)

| Symbol                                                | Parameter Condition                         |                                                            | Min  | Тур   | Max  | Units |

|-------------------------------------------------------|---------------------------------------------|------------------------------------------------------------|------|-------|------|-------|

| NEGATIVE                                              | OUTPUT VOLTAGE CHARGE P                     | PUMP                                                       |      |       |      | •     |

| F <sub>CP</sub>                                       | Negative Charge Pump<br>Switching Frequency |                                                            | 0.96 | 1.2   | 1.44 | MHz   |

| V <sub>ON</sub>                                       | Negative Output Voltage<br>Range            | 21 steps, each step<br>100mV                               | -6.0 |       | -4.0 | v     |

| $V_{\text{ON}\_\text{ACC}}$                           | Output Voltage Accuracy                     |                                                            | -1.5 |       | +1.5 | %     |

| V <sub>DROP</sub>                                     | Dropout voltage                             | V <sub>OP</sub> =5V, I <sub>OP</sub> =80mA                 |      | 250   |      | mV    |

|                                                       | Line Regulation                             | V <sub>IN</sub> =2.5V~4.2V,<br>I <sub>OP</sub> =-80mA      |      | 1     |      | %     |

|                                                       | Load Regulation                             | I <sub>ON</sub> =-80mA to -10mA,<br>V <sub>ON</sub> =-5.4V |      | 1     |      | %     |

| $R_{\text{DIS}_N}$                                    | VON Discharge Resistance                    | V <sub>ON</sub> =5.4V                                      | X 1  | 30    |      | Ω     |

| $V_{\text{ENN(H)}}$                                   |                                             |                                                            | 1.2  |       |      | V     |

| $V_{\text{ENN(L)}}$                                   |                                             |                                                            |      |       | 0.4  | V     |

| I <sub>ENN</sub>                                      | ENN Sink Current                            | V <sub>ENN</sub> =2V                                       |      | 10    |      | μA    |

| I <sub>SHORT</sub>                                    | Output Short Current                        |                                                            |      | 0.15  |      | Α     |

| THERMAL S                                             | SHUTDOWN PROTECTION                         |                                                            |      | · · · |      | ·     |

| T <sub>SHUT</sub>                                     | Thermal Shutdown                            | Temperature Rising                                         |      | 140   |      | °C    |

| T <sub>SHUT_HYST</sub> Thermal Shutdown<br>Hysteresis |                                             | Temperature Falling                                        |      | 30    |      | °C    |

### **Electrical Characteristics (Continued)**

#### (The specifications are at T<sub>A</sub>=25°C, $V_{IN}$ = 3.7V, $V_{OP}$ = 5V, $V_{ON}$ = -5V, unless otherwise noted.)

| Symbol           | Parameter                          | Condition                  | Min                  | Тур | Max  | Units |

|------------------|------------------------------------|----------------------------|----------------------|-----|------|-------|

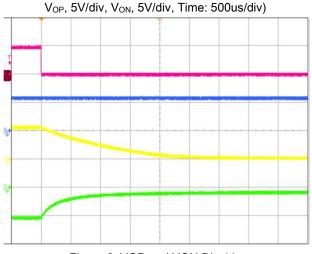

| I2C Compat       | ible Timing Specifications (SCL, S | SDA), referred to Figure 7 |                      |     |      | 1     |

| 4                |                                    | Standard Mode              |                      |     | 100  | kHz   |

| f <sub>SCL</sub> | SCL clock frequency                | Fast Mode                  |                      |     | 400  | kHz   |

|                  | Low paried of the COL starts       | Standard Mode              | 4.7                  |     |      | us    |

| <b>t</b> LOW     | Low period of the SCL clock        | Fast Mode                  | 1.3                  |     |      | us    |

|                  | Lligh paried of the CCL clearly    | Standard Mode              | 4.0                  |     |      | us    |

| <b>t</b> high    | High period of the SCL clock       | Fast Mode                  | 0.6                  |     |      | us    |

| 4                | Bus free time between a            | Standard Mode              | 4.7                  |     |      | us    |

| t <sub>BUF</sub> | STOP and START condition           | Fast Mode                  | 1.3                  |     |      | us    |

|                  | Hold time for a repeated           | Standard Mode              | 4.0                  |     |      | us    |

| <b>t</b> hd, sda | START condition                    | Fast Mode                  | 0.6                  | 5   |      | us    |

| 4                | Data actus tima                    | Standard Mode              | 0.25                 |     |      | us    |

| <b>t</b> su, dat | Data setup time                    | Fast Mode                  | 0.1                  |     |      | us    |

| 4                | Data hold time                     | Standard Mode              | 0.05                 |     | 3.45 | us    |

| <b>t</b> hd, dat | Data noid time                     | F <mark>as</mark> t Mode   | 0.05                 |     | 0.9  | us    |

| 4                | Disc time of CDA signal            | Standard Mode              | 20+0.1C <sub>B</sub> |     | 1000 | ns    |

| t <sub>rda</sub> | Rise time of SDA signal            | Fast Mode                  | 20+0.1C <sub>B</sub> |     | 300  | ns    |

| 4                |                                    | Standard Mode              | 20+0.1C <sub>B</sub> |     | 300  | ns    |

| <b>t</b> fda     | Fall time of SDA signal            | Fast Mode                  | 20+0.1C <sub>B</sub> |     | 300  | ns    |

| <b>t</b> au c=-  | Setup time for STOP                | Standard Mode              | 4.0                  |     | -    |       |

| tsu,sto          | condition                          | Fast Mode                  | 0.6                  |     | -    |       |

| Св               | Capacitive load for SCL and SDA    |                            | -                    | -   | 0.2  | nF    |

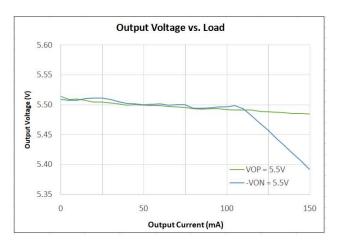

## **Typical Characteristics**

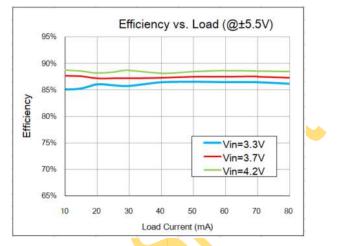

VIN=3.7V, VOP=5V, VON=-5V, TA=+25°C, unless otherwise noted.

Figure 1. Positive and Negative Output Voltage Load Line  $(V_{IN} = 3.7V, V_{OP} = V_{ON} = 5.5V)$

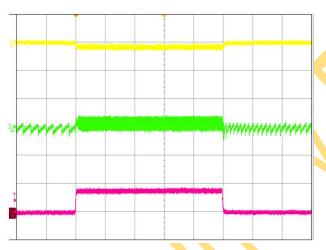

Figure 3. Load Transient Response (CH1: V<sub>OP</sub>, 100mV/div, CH2: VON, 100mV/div, CH3: lout, 100mA/div, Time: 500us/div)

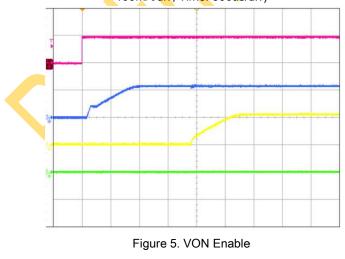

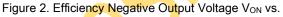

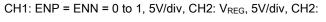

$\label{eq:chi} \begin{array}{l} \mbox{CH1: ENP = ENN = 0 to 1, 5V/div, CH2: V_{REG}, 5V/div, CH2:} \\ \mbox{V}_{OP}, 5V/div, V_{ON}, 5V/div, Time: 500us/div) \end{array}$

#### Figure 4. VOP and VON Enable

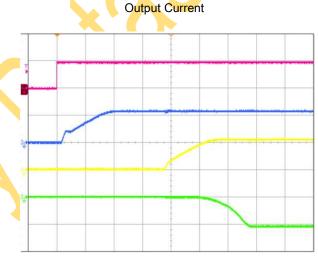

Figure 6. VOP and VON Disable

CH1: ENP = ENN = 1 to 0, 5V/div, CH2:  $V_{REG}$ , 5V/div, CH2:  $V_{OP}$ , 5V/div,  $V_{ON}$ , 5V/div, Time: 500us/div)

### **Detailed Description**

#### **Overview**

The LP6280S supports input voltage range from 2.7 V to 5.5 V, operates with a single inductor scheme to provide a high efficiency with a small solution size. The synchronous boost converter generates a positivevoltage that is regulated down by an integrated LDO, providing the positive supply rail ( $V_{OP}$ ). The negativesupply rail ( $V_{ON}$ ) is generated by an integrated negative charge pump (or CPN) driven from the boost converter output pin REG.

#### Undervoltage Lockout (UVLO)

The LP6280S integrates an undervoltage lockout block (UVLO) that enables the device once the voltage on the VIN pin exceeds the UVLO threshold. No output voltage will be generated as long as the enable signals are not pulled HIGH. The device, as well as all converters (Boost converter, LDO, CPN), will be disabled as soon as the VIN voltage falls below the UVLO threshold.

#### **Power Enable**

The LDO (VOP) and the negative charge pump (VON) are turned on/off by external enable signals. ENP pin is enable control input for VOP and ENN is enable control input for VON. If any enable signal is pulled high, Boost will be enabled once V<sub>IN</sub> meets UVLO voltage level.

#### **Boost Converter**

The LP6280S integrates a PWM synchronous Boost converter operating with current mode control and 1.2MHz (typ) switching frequency. The device is designed for high efficiency over wide output current range.

#### **VOP and VON Discharge**

When VIN falls below UVLO threshold or both ENP and ENN pins are pulled low, all regulators will be turned off. If both ENP and ENN go low, VOP and VON will be actively discharged to GND.

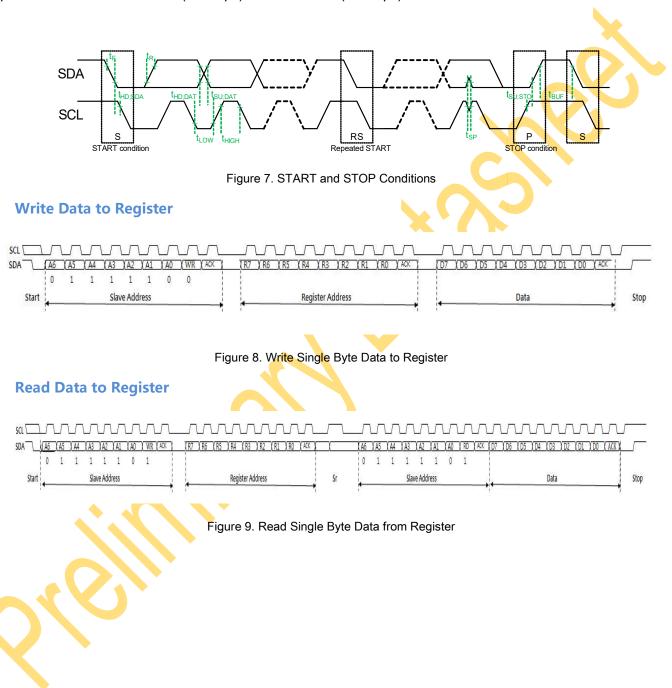

#### **Power Sequencing**

The LP6280S Boost powers up if any of ENP and ENN is pulled high. If the Boost powers up successfully within 2ms, Boost Power Good signal is sent to enable VOP and/or VON rail(s). VOP startup time is about 1ms and VON startup time is about 1.5ms. VOP and VON rails can be enabled sequentially or simultaneously. Similarly, VOP and VON rails can be disabled sequentially or simultaneously. Boost powers off only when both ENP and ENN are pulled low.

#### **Thermal Shutdown Protection**

The LP6280S device enters over temperature protection if its junction temperature exceeds 140°C (typical). During over temperature protection the device is shut down. Once the junction temperature falls below the hysteresis threshold, the device restarts.

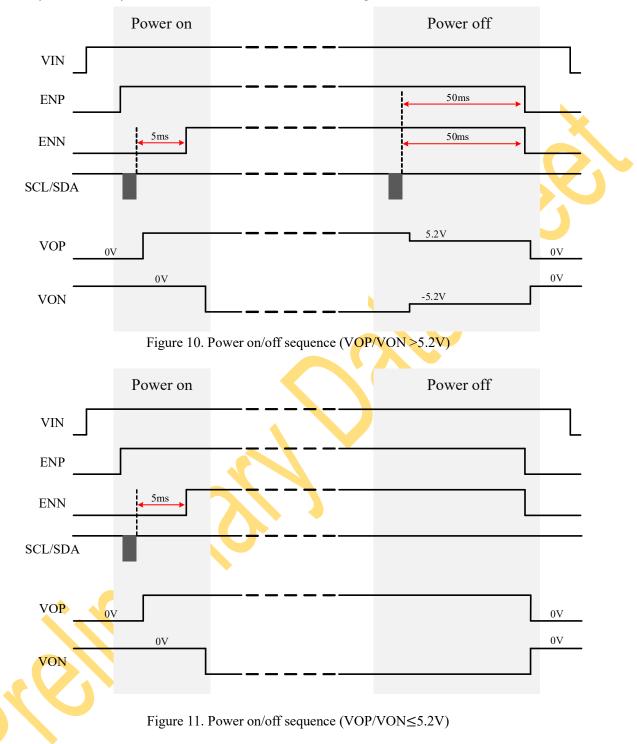

#### **I2C Interface Specification**

The LP6280S can easily modify parameters by I2C bus and the slave address is 0x3E. I2C is a two wire serial interface developed, the bus consists of a clock line (SCL) and a data line (SDA) with pull-up structures. The LP6280S works as a slave mode, and address is 0x3E. The data transfer protocol follow I2C-Bus Specification's standard mode (100kbps) and fast mode (400kbps).

### **Register Maps**

| Address | Description            | Default | D7   | D6 | D5 | D4        | D3 | D2 | D1   | D0   |     |

|---------|------------------------|---------|------|----|----|-----------|----|----|------|------|-----|

| 00H     | SetVOP Voltage         | 0x0F    |      | -  |    | VOP [4:0] |    |    |      |      |     |

| 01H     | SetVON Voltage         | 0x0F    |      | -  |    | VON [4:0] |    |    |      |      |     |

| 03H     | Set Discharge Resistor | 0x03    |      |    |    |           |    |    | DIS_ | DIS_ |     |

| 030     | Enable                 | 0x03    | 0x03 |    |    |           |    |    |      | VOP  | VON |

| FFH     | Set Control Register   | 0x00    | WR   |    |    |           |    |    |      | -    |     |

#### Set VOP Voltage (Register Address - 00H)

| VOP Voltag                                              | VOP Voltage |    |        |         |         |         |         |  |  |  |  |  |

|---------------------------------------------------------|-------------|----|--------|---------|---------|---------|---------|--|--|--|--|--|

| Addr: 00H Default Value: VON Register=0x0F, (VOP =5.5V) |             |    |        |         |         |         |         |  |  |  |  |  |

| D7                                                      | D6          | D5 | D4     | D3      | D2      | D1      | D0      |  |  |  |  |  |

| R                                                       | R           | R  | R/W    | R/W     | R/W     | R/W     | R/W     |  |  |  |  |  |

| 0                                                       | 0           | 0  | VOP[4] | VOP [3] | VOP [2] | VOP [1] | VOP [0] |  |  |  |  |  |

| VOP [4:0] |          |          |          |

|-----------|----------|----------|----------|

| Register  | Volt (V) | Register | Volt (V) |

| 00000     | 4.00     | 10000    | 5.60     |

| 00001     | 4.10     | 10001    | 5.70 人   |

| 00010     | 4.20     | 10010    | 5.80     |

| 00011     | 4.30     | 10011    | 5.90     |

| 00100     | 4.40     | 10100    | 6.00     |

| 00101     | 4.50     | 10101    | Reserved |

| 00110     | 4.60     | 10110    | Reserved |

| 00111     | 4.70     | 10111    | Reserved |

| 01000     | 4.80     | 11000    | Reserved |

| 01001     | 4.90     | 11001    | Reserved |

| 01010     | 5.00     | 11010    | Reserved |

| 01011     | 5.10     | 11011    | Reserved |

| 01100     | 5.20     | 11100    | Reserved |

| 01101     | 5.30     | 11101    | Reserved |

| 01110     | 5.40     | 11110    | Reserved |

| 01111     | 5.50     | 11111    | Reserved |

#### Set VON Voltage (Register Address – 01H)

| VON Voltag                                                | VON Voltage |    |        |         |         |         |         |  |  |  |  |  |  |

|-----------------------------------------------------------|-------------|----|--------|---------|---------|---------|---------|--|--|--|--|--|--|

| Addr: 01H Default Value : VON(Register)=0x0FH, VON =-5.5V |             |    |        |         |         |         |         |  |  |  |  |  |  |

| D7                                                        | D6          | D5 | D4     | D3      | D2      | D1      | D0      |  |  |  |  |  |  |

| R                                                         | R           | R  | R/W    | R/W     | R/W     | R/W     | R/W     |  |  |  |  |  |  |

| 0                                                         | 0           | 0  | VON[4] | VON [3] | VON [2] | VON [1] | VON [0] |  |  |  |  |  |  |

### **Register Maps (Continued)**

| VON[4:0] |                 |       |          |  |  |  |  |

|----------|-----------------|-------|----------|--|--|--|--|

| Register | gister Volt (V) |       | Volt (V) |  |  |  |  |

| 00000    | -4.00           | 10000 | -5.60    |  |  |  |  |

| 00001    | -4.10           | 10001 | -5.70    |  |  |  |  |

| 00010    | -4.20           | 10010 | -5.80    |  |  |  |  |

| 00011    | -4.30           | 10011 | -5.90    |  |  |  |  |

| 00100    | -4.40           | 10100 | -6.00    |  |  |  |  |

| 00101    | -4.50           | 10101 | Reserved |  |  |  |  |

| 00110    | -4.60           | 10110 | Reserved |  |  |  |  |

| 00111    | -4.70           | 10111 | Reserved |  |  |  |  |

| 01000    | -4.80           | 11000 | Reserved |  |  |  |  |

| 01001    | -4.90           | 11001 | Reserved |  |  |  |  |

| 01010    | -5.00           | 11010 | Reserved |  |  |  |  |

| 01011    | -5.10           | 11011 | Reserved |  |  |  |  |

| 01100    | -5.20           | 11100 | Reserved |  |  |  |  |

| 01101    | -5.30           | 11101 | Reserved |  |  |  |  |

| 01110    | -5.40           | 11110 | Reserved |  |  |  |  |

| 01111    | -5.50           | 11111 | Reserved |  |  |  |  |

### Set Discharge Resistor Enable (Register Address - 03H)

| Discharged Resistor Enable/Disable               |    |    |    |    |    |         |         |  |

|--------------------------------------------------|----|----|----|----|----|---------|---------|--|

| Addr: 03H Default Value : DIS_VO(Register)=0x03H |    |    |    |    |    |         |         |  |

| D7                                               | D6 | D5 | D4 | D3 | D2 | D1      | D0      |  |

| R                                                | R  | R  | R  | R  | R  | R/W     | R/W     |  |

| 0                                                | 0  | 0  | 0  | 0  | 0  | DIS_VOP | DIS_VON |  |

| DIS_VOP  |         | DIS_VON  |          |  |  |  |

|----------|---------|----------|----------|--|--|--|

| Register | DIS_VOP | Register | DISP_VON |  |  |  |

| 0        | Disable | 0        | Disable  |  |  |  |

| 1        | Énable  | 1        | Enable   |  |  |  |

#### Set Control Register (Register Address – FFH)

| Control Register                                                          |    |    |    |    |    |    |    |  |

|---------------------------------------------------------------------------|----|----|----|----|----|----|----|--|

| Addr: FFH Write : Control(Register)=0x80H, Read : Control(Register)=0x00H |    |    |    |    |    |    |    |  |

| D7                                                                        | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

| R/W                                                                       | R  | R  | R  | R  | R  | R  | R  |  |

| W_EPROM                                                                   | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

| W_EPROM  |                                                    |

|----------|----------------------------------------------------|

| Register | Bit Description                                    |

| 0        | Disable any registers data write into the EPROM    |

| 1        | Enable all register's data to write into the EPROM |

### **Application Information**

The device can be used for any applications that require positive and negative supplies, ranging from  $\pm 4V$  to  $\pm 6V$  and current up to 80mA. The positive and negative output voltages are independently programmable by I2C interface and their sequencing is also independently programmable by external signals at ENP and ENN pins.

#### **Boost Input Capacitor Selection**

10µF or higher values of low ESR ceramic capacitors are recommended at input VIN pin. A minimum effective capacitance of 4µF is required at VIN pin. Considering capacitance de-rating with higher temperature and DC bias voltages, X7R and 10V or 16V voltage rating are recommended.

#### **Boost Inductor Selection**

A 4.7µH inductor is recommended as shown in the table of Recommended Operating Conditions. In general, lower inductor DCR and larger inductor size support higher Boost conversion efficiency.

#### **Boost Output Capacitor Selection**

10μF or higher values of low ESR ceramic capacitors are recommended as shown in the table of Recommended Operating Conditions. A minimum effective capacitance of 4μF is required. Higher capacitor values and higher voltage ratings can be used to improve load transient response.

#### LDO Output Capacitor Selection

10μF or higher values of low ESR ceramic capacitors are recommended as shown in the table of Recommended Operating Conditions. A minimum effective capacitance of 4μF is required. Higher capacitor values and higher voltage ratings can be used to improve load transient response.

#### **Charge Pump Output Capacitor Selection**

10μF or higher values of low ESR ceramic capacitors are recommended as shown in the table of Recommended Operating Conditions. A minimum effective capacitance of 4μF is required. Higher capacitor values and higher voltage ratings can be used to improve load transient response.

### Flying Capacitor Selection

A 2.2 $\mu$ F low ESR ceramic capacitor is recommended as shown in the table of Recommended Operating Conditions. Flying capacitor values directly impact the VON output voltage accuracy and load transient response. A minimum effective capacitance of 0.9 $\mu$ F is required at a DC bias of V<sub>ON</sub> + 0.3V. For proper operation, the flying capacitor effective value must be lower than the Boost effective output capacitance.

#### **Power-on and Power-off Sequence**

If VOP and VON target voltages are set at higher than 5.2V, the power-on and power-off sequence is recommended as shown in Figure 10. If VOP and VON target voltages are set at lower than or equal to 5.2V, the

power-on and power-off sequence is recommended as shown in Figure 11.

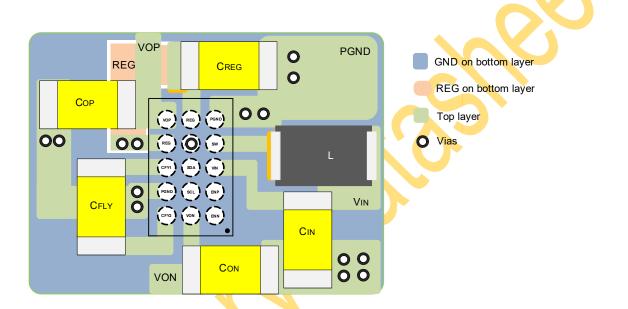

#### **PCB Layout Guideline**

Appropriate PCB layout is important in the power supply design. Good PCB layout minimizes EMI and allows very good output voltage regulation. The following PCB layout guidelines are recommended.

Decouple VIN, REG, VOP and VON pins to PGND on the top layer and place decoupling capacitors as close to the pins as possible. Always avoid vias when possible because they have high inductance and resistance. If vias are necessary, always use more than one in parallel to decrease parasitics especially for power traces.

- 2. Connect AGND and PGND ground together with at least one uninterrupted ground plane, which include power ground and analog ground.

- 3. Place the flying capacitor as close as possible to the CFY1 and CFY2 pins and connect flying capacitors to the IC pins with short and wide traces.

- 4. Minimize trace length of SW node if possible to help reduce EMI emissions and noise that may couple into other portions of the converter.

An example of 2-layer PCB layout is shown in Figure 12.

Figure 12. PCB Layout Example

## **Package Information**

WLCSP-15-ball Package (1.17×1.94) pitch 0.4 (Unit: mm)

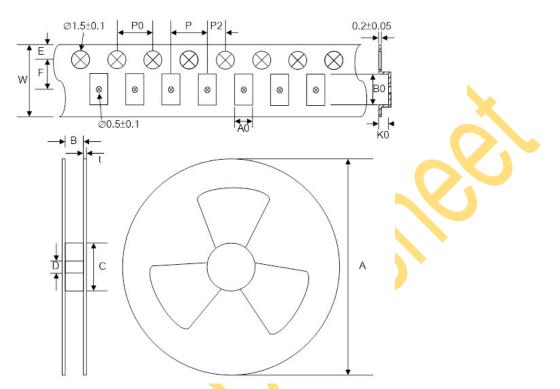

## **Carrier information**

| Device  | Package Type |          | Pins     | SPQ    | A (mm)    | B (mm)    | C (mm)    | D (mm)  | t (mm)   |

|---------|--------------|----------|----------|--------|-----------|-----------|-----------|---------|----------|

|         | WLCSP        |          | 15       | 3000   | ø180±1    | 9.5±0.5   | Ø60±1     | Ø13±0.2 | 1.1±0.25 |

| LP6280S | W (mm)       | E (mm)   | F (mm)   | P (mm) | A0 (mm)   | B0 (mm)   | K0 (mm)   | P0 (mm) | P2 (mm)  |

|         | 8±0.3        | 1.75±0.1 | 3.5±0.05 | 4      | 1.82±0.05 | 2.74±0.05 | 0.75±0.05 | 4       | 2        |