### **Features**

- Wide input voltage range: 4.2V 18V

- Output voltage range: V<sub>ref</sub> − 7V

- High efficiency operation

- Integrated an 60-m $\Omega$  LS-MOSFET and an 90-m $\Omega$  HS-MOSFET

- 91% efficiency at 2A load from 12V to 5V conversion

- · Automatic PFM mode at light load

- ±1% Vref accuracy

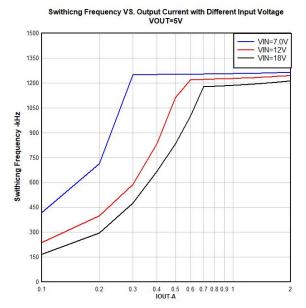

- Typical 1.2-MHz switching frequency

- COT control scheme with fast load transient response

- Hiccup protection

- Integrated UVLO, OVP, OCP, SCP, and OTP protections

- 1.25ms typical soft-start time

- 1.6mm X 1.6mm SOT563 package

- RoHS Compliant and 100% Lead (Pb) Free

#### •

## **Applications**

- Industrial PC

- Network/digital video recorder (NVR/DVR)

- TV and TV box

- 12V Industrial bus applications

### **General Description**

The LP6452AT/F is a synchronous buck converter supporting up to 2A output current. The LP6452AT/F employs an adaptive constant-on-time (COT) control scheme to achieve fast load transient response. The external components are minimized, requiring only one inductor, two resistors, and two capacitors.

The LP6452AT/F supports both aluminum polymer capacitors and ceramic capacitors without extra compensation components.

The LP6452AT/F integrates PFM (Pulse Frequency Modulation) operation, which helps maintain the system efficiency at light load. The LP6452AT/F also integrates multiple protection functions, i.e., over-current protection (OCP), over-temperature protection (OTP), under-voltage lockout (UVLO), and short circuit protection (SCP).

The LP6452AT/F is available in a small 6-pin 1.6mmX1.6mm SOT563 package.

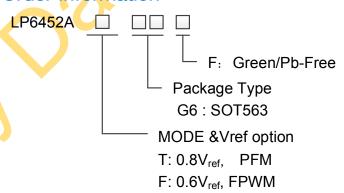

## Order Information

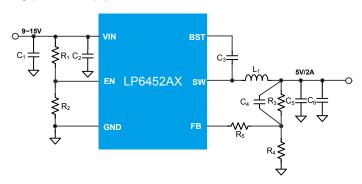

## **Typical Application Circuit**

## **Device Information**

| Part Number | Top Marking | Vref | Mode    | Package | Shipping | MSL     |

|-------------|-------------|------|---------|---------|----------|---------|

| LP6452ATG6F | AgYW        | V8.0 | PFM/PWM | SOT563  | 3K/REEL  | LEVEL 3 |

| LP6452AFG6F | AeYW        | 0.6V | FPWM    | SOT563  | 3K/REEL  | LEVEL 3 |

| LP6452AG6F  | AfYW        | 0.6V | PFM/PWM | SOT563  | 3K/REEL  | LEVEL 3 |

Marking indication: Y: Year code. W: Week code. X: Batch numbers. MSL: Moisture Sensitivity Level according to JEDEC Standard

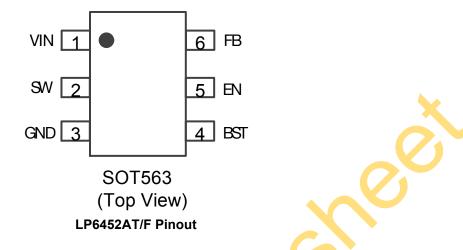

# Pin Diagram

# **Pin Description**

| Pin #<br>LP6452AT/F | Name | Description                                                                                                                     |  |  |  |

|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                   | VIN  | IC power supply input.                                                                                                          |  |  |  |

| 2                   | SW   | The switching node of the converter.                                                                                            |  |  |  |

| 3                   | GND  | Power ground of the IC                                                                                                          |  |  |  |

| 4                   | BST  | Bootstrap pin. Power supply for high-side MOSFET gate driver. A 0.1-µF capacitor must be connected between this pin and SW pin. |  |  |  |

| 5                   | EN   | Enable input. This pin can be used to control the system power sequence as well                                                 |  |  |  |

| 6                   | FB   | Feedback pin. Use a resistor divider to set the desired output voltage                                                          |  |  |  |

# Absolute Maximum Ratings (Note)

| VIN, SW, and EN to GND                           | 0.3V to 19V   |

|--------------------------------------------------|---------------|

| FB to GND                                        | -0.3V to 6.5V |

| BST to SW                                        | -0.3V to 6.5V |

| SW to GND (5ns transient)                        | 3.5V to 20V   |

| Operating Ambient Temperature Range (TA)         | 40°C to 85°C  |

| Maximum Soldering Temperature (at leads, 10 sec) | 260℃          |

**Note**: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ESD Ratings**

| HBM (Human Body Model)     |   | 2kV   |

|----------------------------|---|-------|

|                            |   | 500)/ |

| CDM (Charged-device Model) | 7 | 500V  |

### Thermal Information

θ<sub>JA</sub> (Junction-to-Ambient Thermal Resistance) ------ 140°C/W

## **Recommended Operating Conditions**

| SYMBOL           | PARAMETER                  | MIN              | TYP | MAX | UNIT |

|------------------|----------------------------|------------------|-----|-----|------|

| V <sub>IN</sub>  | Input voltage              | 4.2              |     | 18  | V    |

| V <sub>OUT</sub> | Output voltage             | V <sub>ref</sub> |     | 7   | V    |

| L                | Inductor                   | 0.7              |     | 6.0 | μH   |

| T <sub>A</sub>   | Ambient temperature range  | -40              |     | 85  | °C   |

| C <sub>IN</sub>  | Input decoupling capacitor | 4.7              |     | 100 | μF   |

| Соит             | Output capacitor           | 10               |     | 100 | μF   |

## **Electrical Characteristics**

Version: 3/5/2023

(The specifications are measured under conditions  $V_{IN} = 12V$ ,  $T_J = 25$ °C, unless otherwise specified.)

| SYMBOL              | PARAMETER                             | TEST CONDITIONS                   | MIN   | TYP | MAX   | UNIT |  |  |

|---------------------|---------------------------------------|-----------------------------------|-------|-----|-------|------|--|--|

| INPUT SEC           | NPUT SECTION                          |                                   |       |     |       |      |  |  |

| V <sub>ULVO_R</sub> | Input under voltage lockout threshold | V <sub>IN</sub> rising threshold  |       | 4.0 | 4.2   | V    |  |  |

| Vulvo_H             | UVLO hysteresis                       | V <sub>IN</sub> falling threshold |       | 0.3 |       | V    |  |  |

| I <sub>q_VIN</sub>  | Input quiescent current               | No switching, EN=3V, FB=1.0V      |       | 320 |       | μА   |  |  |

| BUCK CON            | BUCK CONVERTER                        |                                   |       |     |       |      |  |  |

| I <sub>LIM</sub>    | Low-side valley current limit         | T <sub>J</sub> =25°C              | 2.2   | 3.0 | 4.0   | А    |  |  |

| V <sub>ref</sub>    | Reference voltage                     | T <sub>J</sub> =25°C, LP6452AF    | 0.594 | 0.6 | 0.606 | V    |  |  |

|                         |                                      | T <sub>J</sub> =25°C, LP6452AT           | 0.792 | 0.8  | 0.808 | V   |

|-------------------------|--------------------------------------|------------------------------------------|-------|------|-------|-----|

| R <sub>dson_HS</sub>    | High-side FET on resistance          | V <sub>IN</sub> =12V                     |       | 90   |       | mΩ  |

| R <sub>dson_LS</sub>    | Low-side FET on resistance           | V <sub>IN</sub> =12V                     |       | 60   |       | mΩ  |

| F <sub>sw</sub>         | Switching frequency                  |                                          |       | 1200 | X     | kHz |

| t <sub>on-min</sub>     | Minimum<br>on-time <sup>[1]</sup>    |                                          |       | 50   |       | ns  |

| t <sub>off-min</sub>    | Minimum<br>off-time <sup>[1]</sup>   | V <sub>FB</sub> =V <sub>ref</sub> - 0.2V |       | 100  |       | ns  |

| t <sub>on-hiccup</sub>  | Hiccup on time <sup>[1]</sup>        |                                          |       | 2    |       | ms  |

| t <sub>off-hiccup</sub> | Hiccup waiting time <sup>[1]</sup>   |                                          |       | 32   |       | ms  |

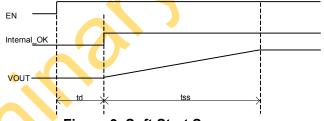

| t <sub>d</sub>          | EN delay time <sup>[1]</sup>         | From EN high to first switching          | 0     | 250  |       | us  |

| t <sub>ss</sub>         | Soft-start time[1]                   | From first switching to 95%Vref          |       | 1.25 |       | ms  |

| T <sub>jsd</sub>        | Thermal shutdown threshold           | Rising threshold                         |       | 160  |       | °C  |

|                         | Thermal shutdown threshold           | Falling threshold                        |       | 135  |       | °C  |

| I <sub>leak_FB</sub>    | FB pin leakage current               |                                          |       | 0.01 |       | μΑ  |

| EN Logic                |                                      |                                          |       |      |       |     |

| V <sub>H</sub>          | EN pin logic high threshold          | EN Rising threshold                      |       | 1.2  |       | V   |

| V <sub>hys</sub>        | EN pin threshold hysteresis          |                                          |       | 0.2  |       | V   |

|                         | EN pin internal pull-down resistance |                                          |       | 1000 |       | kΩ  |

resistance | [1]: Not production tested. Guaranteed by design

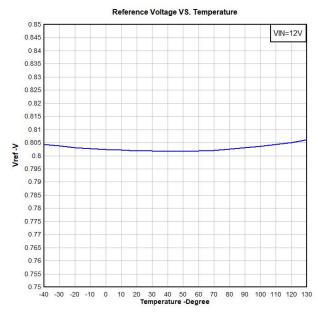

# **Typical Characteristics**

Figure 1. Reference voltage VS. Junction Temperature

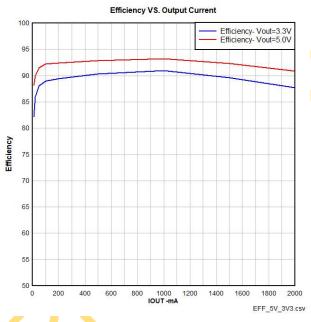

Figure 3. VIN=12V, Efficiency, L=2.2uH, DCR=25m $\Omega$

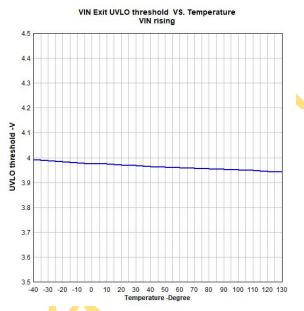

Figure 2. VIN UVLO VS. Junction Temperature

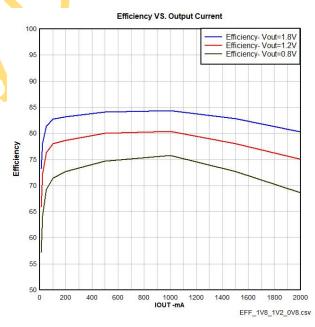

Figure 4. VIN=12V, Efficiency, L=1uH, DCR=15m $\Omega$

Figure 5. Switching Frequency VS. Output Current

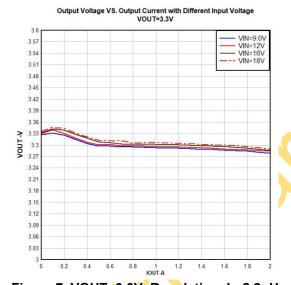

Figure 7. VOUT=3.3V, Regulation, L=2.2uH

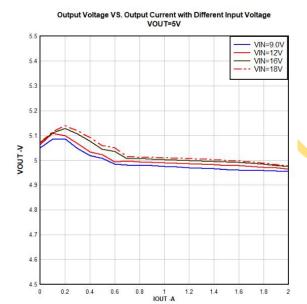

Figure 6. VOUT=5V, Regulation, L=2.2uH

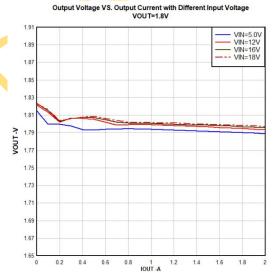

Figure 8. VOUT=1.8V, Regulation, L=1uH

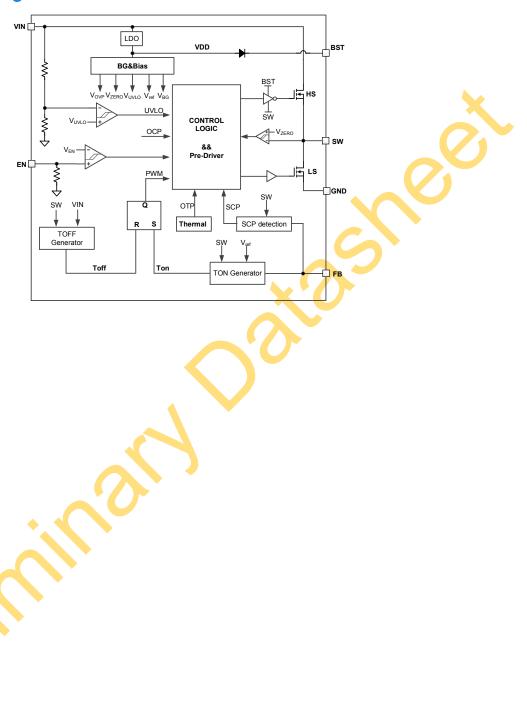

# **Functional Block Diagram**

## **Detailed Description**

#### **Overview**

The LP6452AT/F is a 2A synchronous buck converter, supporting 4.2-18V input voltage range. The adaptive COT control scheme enables fast transient respond and minimizes the output capacitance. The LP6452AT/F supports both aluminum polymer capacitors and low-ESR ceramic capacitors without external compensation circuit. The LP6452AT/F automatically transfers between PFM and PWM according to the output current.

### **Under Voltage Lockout (UVLO)**

When the input voltage VIN is lower than the UVLO threshold, all functions are shut down. When the input voltage is higher than the UVLO rising threshold, the LP6452AT/F can be enabled by the EN pin.

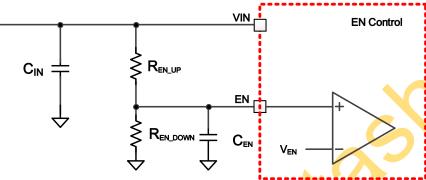

#### **EN Control**

The EN pin can be used to control the system power-up sequence. A precise voltage reference is used as the threshold. When the VIN is above the UVLO threshold and EN voltage rises above the EN pin logic high threshold (1.2V typically), the LP6452AT/F enables all the internal circuits, delays for 260us, and begins the soft-start (refer to Soft-start section for more details).

The EN pin has an internal 1000kΩ pull-down resistor to ground.

#### Soft-start

The LP6452AT/F integrates soft-start function with a typical time of 1.25ms(  $t_{ss}$ ). After passing the UVLO threshold and enabled by the EN pin with the 250us delay( $t_d$ ), the internal reference voltage ramps from zero to the Vref in 1.25-ms and the output voltage ramps up accordingly.

Figure 9. Soft Start Sequence

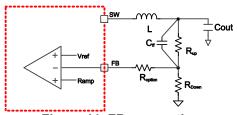

### Constant-ON Time (COT) Control Scheme

The LP6452AT/F integrates the COT control scheme for pseudo-fixed- frequency operation when operating in continuous conduction mode (CCM). Refer to the Functional Block Diagram for better understanding of the operation. The internal on-time (TON) generator block monitors the FB-pin voltage and turns on the high-side MOSFET to start a switching cycle, when the FB-pin voltage drops to an internal reference voltage Vref. Then the internal circuits start to calculate the on-time of the high-side MOSFET, which is proportional to the input voltage and inversely proportional to the output voltage. Once the on-time is finished, the TOFF generator turns off the high-side MOSFET and turns on the low-side MOSFET.

#### PFM Operation

The LP6452AT is designed to maintain high efficiency at light load by adopting pulse-frequency modulation (PFM). In the PFM, the switching cycle is still initiated by the TON generator monitoring the FB-pin voltage. The high-side MOSFET is turned on for TON time and then turned off, followed by turning on the low-side MOSFET. The inductor current falls when the low-side MOSFET is on. When the inductor current reaches zero, detected by the zero-current detection (ZCD) comparator, the low-side MOSFET is turned off, together with the high-side MOSFET. Both MOSFETs remains off until a new switching cycle begins, determined by TON generator. As the load current decreases, the

Version: 3/5/2023 www.lowpowersemi.com email: marketing@lowpowersemi.com 9 / 18

duration for both MOSFETs to remain off increases, leading to a lower switching frequency and higher power efficiency.

### **FPWM Operation (LP6452AF)**

The LP6452AF is designed to work at FPWM to maintain the good regulation and transient performance. When the output decreases, the inductor is allowed to flow from the output to the ground plane. In this way, the switching frequency is kept the same even without load.

The FPWM operation mode reduced the output ripple under light load at the cost of lower light load efficiency

### **Bootstrap Capacitor**

The LP6452AT/F integrates two N-MOSFET to achieve high efficiency. The high-side MOSFET is powered by the bootstrap capacitor CBST, which is between the BST pin and SW pin.

#### Over Current Protection and Short Circuit Protection

The LP6452AT/F protects an over current situation by limiting the inductor valley current. The current of low-side MOSFET is monitored all the time to sense the inductor valley current when the LP6452AT/F is enabled. The high-side MOSFET cannot be turned on if the valley current is higher than the low-side valley current limit, protecting the inductor current from further increasing. The inductor current is limited to the valley current limit pluses a half of the inductor ripple current.

The SCP is realized by monitoring the FB-pin voltage when the inductor current is limited. Once the output load draws more current than the current limit, the output voltage drops. When the FB voltage drops to 50% of the Vref for 1.5-ms, the LP6452AT/F shuts down. The LP6452AT/F will restart after a typical 32-ms hiccup waiting time. If the SCP condition still holds after soft-start, the LP6452AT/F shutdown again, repeating the hiccup operation.

When the over current condition is removed, the output voltage returns to normal operation.

#### **Thermal Protection**

The LP6452AT/F has a thermal protection function. The device will shut down when the internal temperature is higher than 160°C and will restart after the temperature drops below 135°C.

Version: 3/5/2023 <u>www.lowpowersemi.com</u> email: <u>marketing@lowpowersemi.com</u> 10 / 18

## **Application Information**

### **Design Requirements**

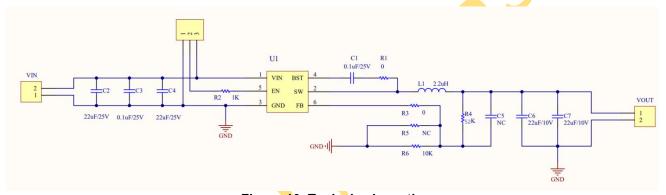

The table 1 shows the design parameters for a typical 5V output voltage in the IPC application.

Table 1 Design Parameters(LP6452AT)

| Parameter           | Target  |  |

|---------------------|---------|--|

| Input voltage range | 9~15V   |  |

| Output voltage      | 5V      |  |

| Transient ripple    | ±200mV  |  |

| Operating frequency | 1200kHz |  |

Figure 10. Typical schematic

## **Output Voltage Setting**

The output voltage can be programmed by adjusting the external resistor divider R<sub>UP</sub> and R<sub>DOWN</sub> according to the equation below:

$$V_{\text{OUT}} = (\frac{R_{\text{UP}}}{R_{\text{DOWN}}} + 1) * V_{ref}$$

When the output voltage is in regulation, the typical voltage at FB pin is 0.8V for LP6452AT.

For better accuracy, the  $R_{DOWN}$  is recommended to be lower than  $100k\Omega$  to ensure the current flowing through  $R_{DOWN}$  is at least 100 times larger than the FB pin leakage current.

For a 5V-output application, a  $10k\Omega$  R<sub>DOWN</sub> is selected and the R<sub>UP</sub> is  $52.5k\Omega$ .

A resistor with higher than  $1k\Omega$  but lower than  $100k\Omega$  should be placed between the resistor divider and FB pin if a  $C_{\rm ff}$  capacitor is soldered.

Figure 11. FB connection

### **EN Design**

The LP6452AT/F allows the user to design a precise VIN voltage to enable the converter during power on. The startup sequence can be designed by adjusting the resistor divider of R<sub>UP\_EN</sub> and R<sub>DOWN\_EN</sub> with the equation below,

$$V_{EN} = \frac{1000 k\Omega / / R_{DOWN\_EN}}{R_{UP\_EN} + 1000 k\Omega / / R_{DOWN\_EN}} * VIN$$

where  $V_{EN}$  is the EN rising threshold voltage at which the converter is enabled, which is 1.2V typically. A 47pF-1nF capacitor is recommend to be soldered in parallel with the  $R_{EN\_DOWN}$  to avoid the high-frequency noise influence from the switching node.

Figure 12. EN connection

### **Inductor and Output Capacitor Setting**

The inductor ripple is calculated by the equation below:

$$I_{PP} = (\frac{V_{OUT}}{L * Fsw} * \frac{V_{IN} - V_{OUT}}{V_{IN}})$$

To get a better efficiency, the inductor ripple is recommended to be controlled under 40% of the output current to minimize the AC loss of the inductor and power MOSFETs.

For a typical 12V input voltage and 5V output voltage, a low DCR value, 2.2-µH inductor is recommended.

The output capacitor not only impacts the output ripple but also the loop stability. Please follow the design rules in the table below. A feedforward capacitor  $C_{FF}$  can be selected to improve the transient behavior. The typical capacitance can be 10-100pF. For this design, 10V, X5R, 22 $\mu$ F capacitors (GRM21BR61A226ME51) from Murata are soldered at the VOUT to GND. Multiple capacitors should be soldered to keep the system stable because of the voltage rating effect.

Table 2 Recommend R/L/C values(LP6452AT)

| Vout | Inductor-L   | Cout                           | Rup     | R <sub>DOWN</sub> | Roption | C <sub>ff</sub> |

|------|--------------|--------------------------------|---------|-------------------|---------|-----------------|

| 1.2V | 1μΗ/1.2μΗ    | 22µF*1                         | 5 kΩ    | 10 kΩ             | 0 Ω     | NA              |

| 3.3V | 1.5μH/2.2μH  | 22µF*2                         | 31 kΩ   | 10 kΩ             | 10 kΩ   | 10-100pF        |

| 5.0V | 2.2µH ~4.7µH | 22µF*3(2.2uH)<br>22µF*2(3.3uH) | 52.5 kΩ | 10 kΩ             | 10 kΩ   | 10-100pF        |

## **Bootstrap** capacitor

A 0.1-μF ceramic capacitor is needed to supply power for the high-side N-MOSFET driver. The capacitor should be at least 10V.

### Input capacitor

A typical 22- $\mu$ F ceramic capacitor is needed to serve as the bulk capacitor at the VIN pin. An additional 0.1 $\mu$ F is strongly recommended to provide additional high frequency filtering and should be placed to the VIN pin and GND as close as possible.

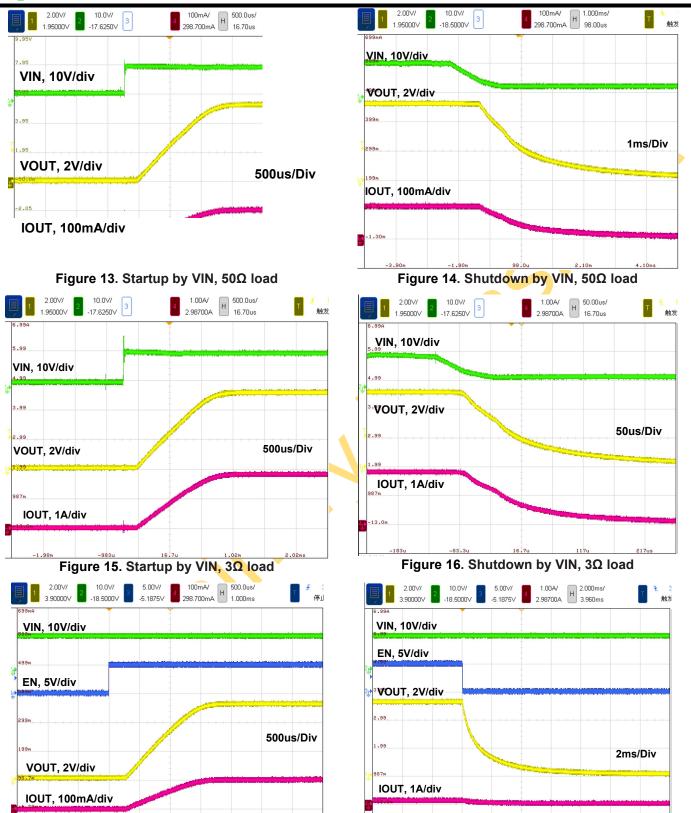

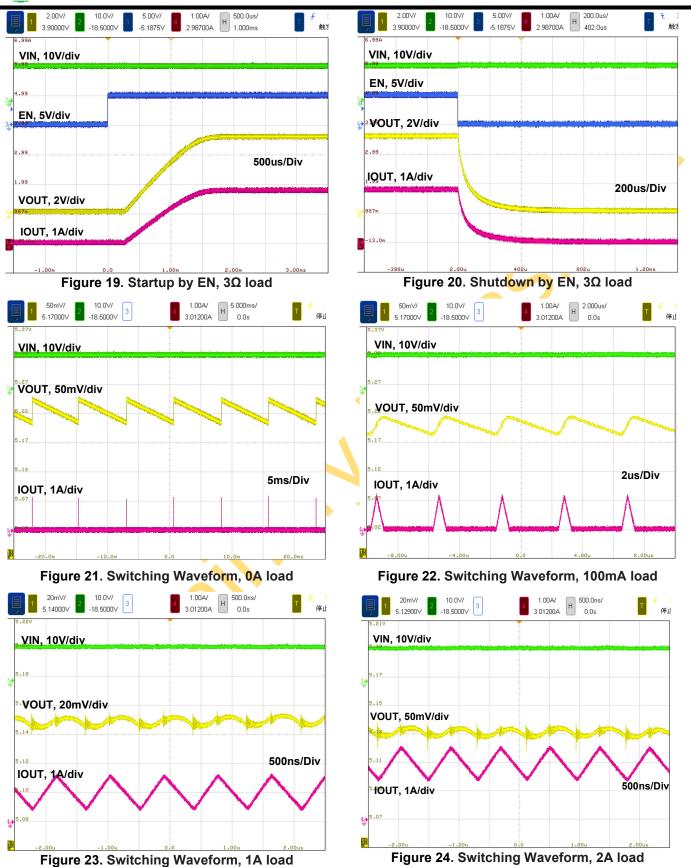

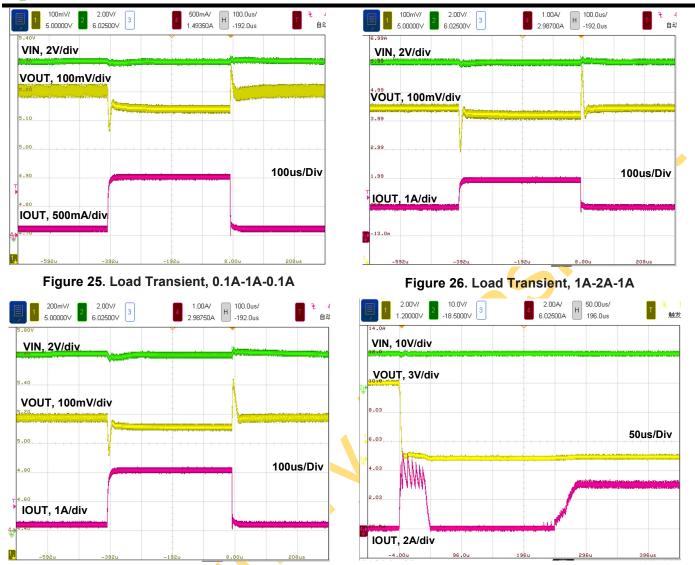

Application Waveforms (Vin=12V, L=2.2uH, Cout=22uF\*3)

Figure 18. Shutdown by EN,  $50\Omega$  load

Figure 17. Startup by EN,  $50\Omega$  load

Figure 27. Load Transient, 0.2A-2A-0.2A

Figure 28. Current Limit Operation

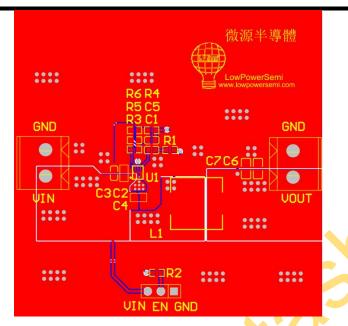

### **PCB Layout Guidelines**

Proper layout of the components to minimize high frequency current path loop is important to prevent electrical and magnetic field radiation and high frequency resonant problems. Follow this specific order carefully to achieve the proper layout.

- Place input capacitor (C<sub>2</sub> and C<sub>4</sub>) as close as possible to VIN pin and GND pin and use shortest copper trace connection or GND plane.

- Put output capacitor near to the inductor output terminal and the device. Ground connections need to be tied to the IC ground with a short copper trace or GND plane

- Place inductor input terminal to SW pin as close as possible and limit SW node copper area to lower electrical and magnetic field radiation. Do not use multiple layers in parallel for this connection. Minimize parasitic capacitance from this area to any other trace or plane.

- $R_1$  is reserved to slow down the switching speed for noise sensitive applications and  $R_3$  with higher than  $1k\Omega$  resistor should be soldered if the feedforward capacitor is soldered at the same time.

Version: 3/5/2023

Figure 29 Layout example

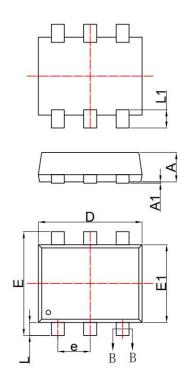

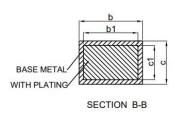

# **Packaging Information**

# 1.6x1.6 SOT563 package

Version: 3/5/2023

| CVANDOL | N     | <b>JILLIMETER</b> | 2    |

|---------|-------|-------------------|------|

| SYMBOL  | MIN   | NOM               | MAX  |

| Α       | 0.53  |                   | 0.60 |

| A1      | 0.00  |                   | 0.05 |

| b       | 0.19  |                   | 0.27 |

| b1      | 0.18  | 0.20              | 0.23 |

| С       | 0.11  |                   | 0.16 |

| c1      | 0.10  | 0.11              | 0.12 |

| D       | 1.50  | 1.60              | 1.70 |

| E       | 1.503 | 1.60              | 1.70 |

| E1      | 1.10  | 1.20              | 1.30 |

| е       |       | 0.50BSC           |      |

| L       | 0.10  | 0.20              | 0.30 |

| L1      | 0.20  | 0.30              | 0.40 |

Revision History

| Revision | Date      | Change Description                                         |

|----------|-----------|------------------------------------------------------------|

| Rev 1p0  | 10/5/2022 | First release version                                      |

| Rev 1p1  | 3/5/2023  | Add "LP6452AG6F" in Device Information Table Add MSL level |