High-Efficiency 3.5A Sensorless Switching Charger

#### **Features**

LowPowerSemi 微源半导体

- Easy-to-use standalone high-efficiency 1-cell switching charger

- Proprietary sensorless technique

- 4.1V to 6.2V input voltage with 28V absolute maximum input voltage rating

- Resistor programmable charge voltages 4.1V/4.2V/4.25V/4.35V

- 3.5A maximum fast charge current

- 1.2MHz switching frequency

- 94% high efficiency @ VBAT=3.8V, ICHG=2A

- 91% high efficiency @ VBAT=3.8V, ICHG=3A

- Input voltage regulation to allow weak input power source to charge battery (VINDPM)

- Support trickle charge, precharge, Constant Current (CC) charge and Constant Voltage (CV) charge, charge termination and recharge

- High charge accuracy

- +/- 0.5% charge voltage regulation

- +/- 6% charge current regulation

- High integration

- Integrated all MOSFETs

- Internal loop compensation

- Internal bootstrap diode

- LED charge indication driver

- Protections

- Cycle-by-cycle current limit protection

- Input under-voltage lockout (UVLO)

- Input over-voltage protection (OVP)

- Cold/hot battery temperature monitoring

- Junction temperature thermal regulation

- Charge safety timer

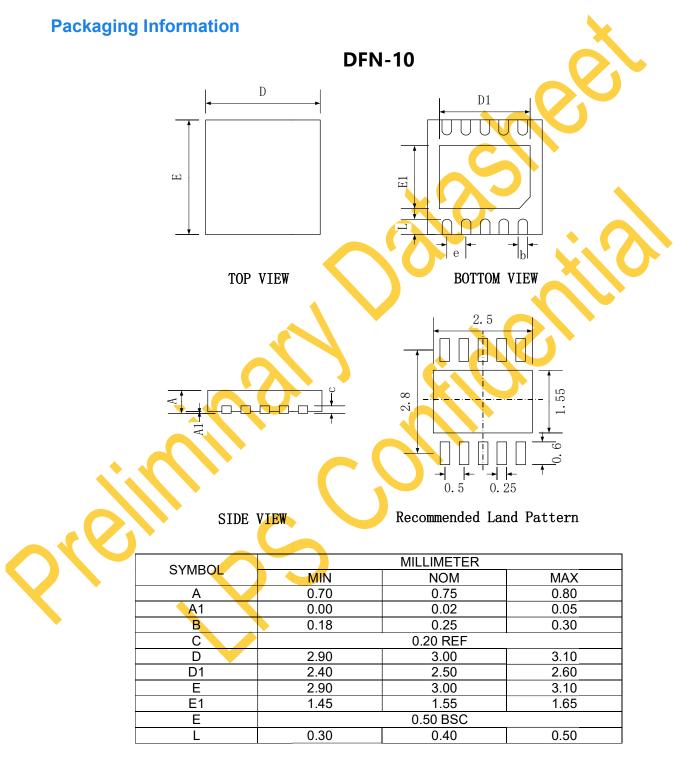

- Packaging

- DFN3x3-10

- RoHS compliant and halogen free

- 100% lead (Pb) free

## **Applications**

- Portable battery powered devices

- Gaming devices

- Charging docks and cradles

• E-Cigarette

## General Description

The LP4034 is a standalone 1-cell switching battery charger providing up to 3.5A charge current to the battery from 4.1V to 6.2V input voltage. The charge current is programmable by a resistor connected from ISET to GND and the charge voltage is programmable by a resistor connected from VSET to GND. The charge can be enabled and disabled from ISET pin. The LP4034 operates at 1.2MHz switching frequency allowing a small-size 1uH inductor for 3.5A fast charging. The integrated current patent-protected sensing technique eliminates external sensing resistor allowing very high charge efficiency, low BOM cost and small footprint. The precharge, fastcharge and termination current accuracy is competitive compared to external-resistor-based current sensing architecture. LP4034 is available in DFN3x3-10 package.

LP4034

####

#### Π. -43

| Part Number                | Top Marking               | Package        | Moisture Sensitivity Level | Shipping |

|----------------------------|---------------------------|----------------|----------------------------|----------|

| LP4034QVF                  | LPS<br>LP4034<br>YWX      | DFN-10         | MSL3                       | 5K/REEL  |

| Marking indication: Y: Yea | ar code. W: Week code. X: | Batch numbers. |                            |          |

|                            |                           |                |                            |          |

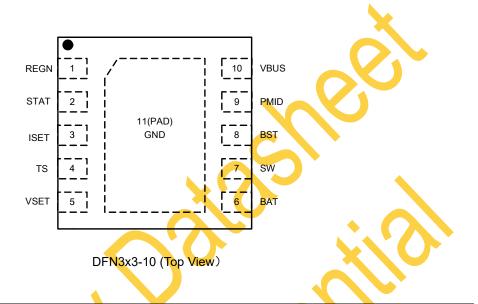

## Pin Diagram

## **Pin Description**

|   | Pin # | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1     | REGN | Positive LDO output. Connect a 2.2µF ceramic capacitor from REGN to GND. The capacitor should be placed close to the IC.                                                                                                                                                                                                                                                                                                                                                                   |

|   | 2     | STAT | <ul> <li>Charge status indication output. Connect a LED from REGN pin to STAT pin via a current limiting resistor. The STAT pin indicates charger status:</li> <li>Charge in progress: STAT pin is pulled LOW</li> <li>Charge complete or charger in SLEEP mode: STAT pin is OPEN</li> <li>Fault mode: STAT pin blinks</li> </ul>                                                                                                                                                          |

|   | 3     | ISET | Charge current program input. Connect a 1% resistor RISET from this pin to ground to program the charge current. If ISET pin is floating or pulled high (>1.3V), charge is disabled. If ISET pin is pulled low, charge is disabled. No capacitor is allowed to connect at this pin.                                                                                                                                                                                                        |

|   | 4     | TS   | Battery temperature sense thermistor input. Charge is suspended if the battery thermistor temperature is out of range. Leave the TS pin floating if TS pin function is not used.                                                                                                                                                                                                                                                                                                           |

| Q | 0     | VSET | Charge voltage setting input. VSET pin sets battery charge/regulation voltage. Program battery regulation voltage with a resistor connected from VSET to GND. No capacitor is allowed to connect at this pin.<br>• RVSET floating (>200k $\Omega$ +/-10%): V <sub>BATREG</sub> = 4.1V<br>• RVSET = 51 k $\Omega$ +/-10%: V <sub>BATREG</sub> = 4.35V<br>• RVSET = 10k $\Omega$ +/-10%: V <sub>BATREG</sub> = 4.25V<br>• RVSET shorted to GND (< 510 $\Omega$ ): V <sub>BATREG</sub> = 4.2V |

|   | 6     | BAT  | Battery connection pin. Connect this pin to node of inductor output terminal and battery pack positive terminal. $\geq$ 10uF capacitor is recommended to connect to this node.                                                                                                                                                                                                                                                                                                             |

|   | 7     | SW   | Switching node. Internally SW node is connected to the source of the n-channel HSFET and the drain of the N-channel LSFET. Connect this pin to a terminal of external inductor.                                                                                                                                                                                                                                                                                                            |

|   | 8     | BST  | High-side MOSFET driver supply input. BST is internally connected to the cathode of the internal boot-strap diode. Connect 47nF bootstrap capacitor from BST to SW.                                                                                                                                                                                                                                                                                                                        |

|   | 9     | PMID | Connected to the drain of the reverse blocking N-channel MOSFET (RBFET) and the drain of high-side MOSFET (HSFET). Place ceramic $10\mu$ F on PMID to GND and place it as close as possible to IC.                                                                                                                                                                                                                                                                                         |

|   | 10    | VBUS | Charger input connection. The internal n-channel reverse block MOSFET (RBFET) is connected between VBUS and PMID with VBUS on source. Place a 1uF ceramic capacitor from VBUS to GND and place it as close as possible to IC.                                                                                                                                                                                                                                                              |

| Γ | 11    | GND  | Power ground and analog ground. The GND is down-bonded to the pad.                                                                                                                                                                                                                                                                                                                                                                                                                         |

---45°C/W

### Absolute Maximum Ratings (Note)

| Absolute Maximum Katings (199                    |               |

|--------------------------------------------------|---------------|

| VBUS, PMID voltage to GND                        |               |

| SW, BAT Voltage to GND                           | 0.3V to 9V    |

| BST to SW Voltage to GND                         | 0.3V to 6V    |

| REGN, STAT, ISET, TS, VSET Voltages to GND       | 0.3V to 6V    |

| STAT Sink Current                                | 6mA           |

| REGN Source Current                              | 16mA          |

| Maximum Junction Temperature (Tj)                | 150°C         |

| Storage Temperature Range                        | 40°C to 150°C |

| Maximum Soldering Temperature (at leads, 10 sec) | 260°C         |

|                                                  |               |

Note: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD** Ratings

| HBM (Human Body Model)       | 2kV  |

|------------------------------|------|

| MM (Machine Model)           | 200V |

|                              | 2001 |

| CDM (Charge Discharge Model) | 500V |

### Thermal Information 🤇

θ<sub>JA</sub> (Junction-to-Ambient Thermal Resistance) ------

## **Recommended Operating Conditions**

| SYMBOL | PARAMETER                                              | MIN  | TYP | MAX  | UNIT |

|--------|--------------------------------------------------------|------|-----|------|------|

| Vin    | Input Voltage                                          | 4.1  |     | 6.2  | V    |

| Існд   | Fast Charge Current                                    | 0.35 |     | 3.5  | A    |

| VBAT   | Battery Charge Voltage                                 | 4.1  |     | 4.4  | V    |

| Та     | Operating Junction Temperature Range (T <sub>J</sub> ) | -40  |     | 125  | °C   |

| ΤΑ     | Ambient Temperature Range                              | -40  |     | 85   | °C   |

| L      | Output Inductance <sup>(1)</sup>                       | 0.7  | 1   | 2.64 | μH   |

| CREGN  | REGN LDO Capacitance <sup>(1)(3)</sup>                 | 1    | 2.2 | 4.7  | μF   |

| CIN    | Input Capacitance <sup>(1)(2)</sup>                    | 0.6  | 1   | 4.7  | μF   |

| Срмір  | PMID Capacitance <sup>(1)(2)</sup>                     | 4    | 10  | 40   | μF   |

| Сват   | BAT Capacitance <sup>(1) (3)</sup>                     | 4    | 10  | 40   | μF   |

Notes:

(1) The values recommended in the table are effective inductance and capacitance.

(2) X7R and 16V or higher voltage rating are recommended.

(3) X7R and 10V or higher voltage rating are recommended.

## **Electrical Characteristics**

(The specifications are at  $V_{VBUS_LOWV} < V_{VBUS} < V_{VBUS_OVP}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ , L=1uH, T<sub>J</sub> = 25°C unless otherwise noted)

| SYMBOL                                     | PARAMETER                                   | 1      |                                                                       | MIN   | TYP                                        | MAX   | UNIT |

|--------------------------------------------|---------------------------------------------|--------|-----------------------------------------------------------------------|-------|--------------------------------------------|-------|------|

| QUIESCENT C                                | URRENT                                      |        |                                                                       |       |                                            |       |      |

| I <sub>Q_BAT</sub>                         | Battery reverse curre                       | ent    | VBAT= VSW = 4.5V, VBUS<br>pin floating                                | 3     |                                            | 1     | μA   |

| I <sub>Q_BAT</sub>                         | Battery leak current                        |        | Charge is terminated,<br>V <sub>BAT</sub> =4.5V                       |       |                                            | 5     | μA   |

| $I_{Q_{BAT}}$                              | Battery leak current                        |        | ISET pin floating,<br>V <sub>BAT</sub> =4.5V                          |       |                                            | 5     | μA   |

| I <sub>Q_BAT</sub>                         | Battery leak current                        |        | ISET pin short, V <sub>BAT</sub> =4.5V                                |       |                                            | 5     | μA   |

| REGN LDO                                   |                                             |        |                                                                       |       |                                            |       | 1    |

| V <sub>REGN</sub>                          | REGN LDO output                             | oltage | V <sub>VBUS</sub> =5V, I <sub>REGN</sub> =16mA                        | 4.2   |                                            | 5.0   | V    |

| I <sub>REGN</sub>                          | REGN LDO o <mark>u</mark> tput o            | urrent |                                                                       |       |                                            | 16    | mA   |

| I <sub>REGN</sub>                          | REGN LDO short cir<br>protection            | cuit   |                                                                       |       | 20                                         |       | mA   |

| MOSFETS                                    |                                             |        |                                                                       |       | ·<br>· · · · · · · · · · · · · · · · · · · | 1     | 1    |

| R <sub>DSON_Q1</sub>                       | RBFET on-resistanc                          | e      | V <sub>VVBUS</sub> =5V                                                |       | 38                                         |       | mΩ   |

| R <sub>DSON_Q2</sub>                       | HSFET on-resistanc                          | e      | V <sub>VVBUS</sub> =5V                                                |       | 55                                         |       | mΩ   |

| R <sub>DSON_Q3</sub>                       | LSFET on-resistanc                          | e      | V <sub>VVBUS</sub> =5V                                                |       | 48                                         |       | mΩ   |

|                                            | GE                                          |        |                                                                       | L.    |                                            |       |      |

| V <sub>VBUS</sub>                          | VBUS operation ran                          | ge     |                                                                       | 4.1   |                                            | 6.2   | V    |

| V <sub>VBUS_LOWV</sub>                     | REGN turn-on thres                          | hold   | V <sub>VBUS</sub> rising                                              | 3.65  | 3.75                                       | 3.85  | V    |

| V <sub>VBUS_LOWV_HYS</sub>                 | REGN turn-on thres                          | hold   | V <sub>VBUS</sub> falling                                             |       | 300                                        |       | mV   |

| V <sub>SLEEP</sub>                         | Into sleep mode three                       | eshold | $V_{VBUS}$ falling, $V_{VBUS}$ - $V_{BAT}$                            | 30    | 60                                         | 90    | mV   |

| V <sub>SLEEPZ</sub>                        | Exit sleep mode three                       | eshold | $V_{VBUS}$ rising, $V_{VBUS}$ - $V_{BAT}$                             | 110   | 150                                        | 250   | mV   |

| VINDPM_MIN                                 | Minimum V <sub>INDPM</sub>                  |        | V <sub>BAT</sub> =3.5V                                                | 3.9   | 4.0                                        | 4.1   | V    |

| VINDPM                                     | VINDPM                                      |        | V <sub>BAT</sub> =4.0V<br>V <sub>INDPM</sub> =V <sub>BAT</sub> +0.25V | 4.175 | 4.25                                       | 4.325 | V    |

| $V_{\text{VBUS}\_\text{OVP}\_\text{RISE}}$ | V <sub>VBUS</sub> input overvolta threshold | •      | V <sub>VVBUS</sub> rising                                             | 6.2   | 6.4                                        | 6.6   | V    |

| V <sub>VVBUS_OVP_HYS</sub>                 | VBUS input overvolt threshold hysteresis    |        | V <sub>VVBUS</sub> falling                                            |       | 0.5                                        |       | V    |

## **Electrical Characteristics**

(The specifications are at  $V_{VBUS_LOWV} < V_{VBUS} < V_{VBUS_OVP}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ , L=1uH, T<sub>J</sub> = 25°C unless otherwise noted)

| SYMBOL                   | PARAMETER                                                      | TEST CONDITIONS                                                              | MIN   | ТҮР  | MAX   | UNIT |

|--------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------|-------|------|-------|------|

| BATTERY C                | HARGER                                                         |                                                                              |       |      |       |      |

|                          |                                                                |                                                                              | 4.079 | 4.1  | 4.121 | V    |

|                          | Charge voltage                                                 |                                                                              | 4.179 | 4.2  | 4.221 | V    |

| V <sub>BATREG</sub>      | regulation                                                     |                                                                              | 4.328 | 4.35 | 4.372 | V    |

|                          |                                                                |                                                                              | 4.22  | 4.25 | 4.273 | V    |

|                          |                                                                | $R_{ISET} = 40k\Omega, V_{VBUS} = 5V, \\ V_{BAT} = 3.8V$                     | 940   | 1000 | 1060  | mA   |

| I <sub>CHG</sub>         | Fast charge current                                            | $R_{ISET} = 20k\Omega, V_{VBUS} = 5V,$ $V_{BAT} = 3.8V$                      |       | 2000 |       | mA   |

|                          |                                                                | R <sub>ISET</sub> = 13.3kΩ, V <sub>VBUS</sub> =5V,<br>V <sub>BAT</sub> =3.8V |       | 3000 |       | mA   |

|                          |                                                                | $R_{ISET} = 40 k\Omega$ , V <sub>VBUS</sub> =5V,<br>V <sub>BAT</sub> =2.5V   | 70    | 100  | 130   | mA   |

| I <sub>PRECHG</sub>      | Precharge current                                              | $R_{ISET} = 20k\Omega, V_{VBUS} = 5V, V_{BAT} = 2.5V$                        |       | 200  |       | mA   |

|                          |                                                                | $R_{ISET} = 13.3 k\Omega, V_{VBUS} = 5V, V_{BAT} = 2.5V$                     |       | 300  |       | mA   |

|                          |                                                                | $R_{ISET} = 40 k\Omega, V_{VBUS} = 5V$                                       | 70    | 100  | 130   | mA   |

|                          | Termination current                                            | $R_{ISET} = 20k\Omega, V_{VBUS} = 5V$                                        |       | 200  |       | mA   |

|                          |                                                                | $R_{ISET} = 13.3 k\Omega, V_{VBUS} = 5V$                                     |       | 300  |       | mA   |

| VBAT_SHORT_R             | V <sub>BAT</sub> short rising<br>threshold                     | Battery short to precharge                                                   | 2.05  | 2.20 | 2.35  | V    |

| IBAT_SHORT               | Trickle charge current                                         | V <sub>VBUS</sub> =5V, V <sub>BAT</sub> =1.0V                                | 50    | 60   | 70    | mA   |

| VBAT_SHORT_F             | V <sub>BAT</sub> short falling<br>threshold                    | Precharge to battery short                                                   | 1.85  | 2.0  | 2.15  | V    |

| V <sub>BAT_LOWV_RI</sub> | V <sub>BAT</sub> fast charge rising<br><sup>SE</sup> threshold | Precharge to fast charge                                                     | 2.9   | 3.0  | 3.1   | V    |

| V <sub>BAT_LOWV_FA</sub> | V <sub>BAT</sub> fast charge falling<br>threshold              | Fast charge to precharge charge                                              | 2.6   | 2.7  | 2.8   | V    |

| V <sub>RECHG_HYS</sub>   | Recharge threshold                                             | V <sub>BAT</sub> falling                                                     |       | 160  |       | mV   |

| STAT                     |                                                                |                                                                              |       |      |       |      |

| f <sub>STAT_BLK</sub>    | Blinking frequency                                             | 50% duty                                                                     |       | 1    |       | Hz   |

| I <sub>STAT PD</sub>     | STAT pull-down current                                         |                                                                              |       |      | 6     | mA   |

## **Electrical Characteristics**

(The specifications are at  $V_{VBUS_LOWV} < V_{VBUS} < V_{VBUS_OVP}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ , L=1uH, T<sub>J</sub> = 25°C unless otherwise noted)

| SYMBOL                   | PARAMETER                                                                                         | TEST CONDITIONS                                             | MIN   | ТҮР   | MAX   | UNIT |

|--------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------|-------|-------|------|

| SWITCHING                | CONVERTER                                                                                         |                                                             |       |       |       |      |

| F <sub>sw</sub>          | Switching Frequency                                                                               |                                                             | 1080  | 1200  | 1320  | kHz  |

| I <sub>HSFET_OCP</sub>   | HSFET Over Current Protection                                                                     |                                                             |       | 5.4   |       | А    |

| I <sub>LSFET_OCP</sub>   | LSFET Reverse Current<br>Protection                                                               |                                                             |       | 1.8   |       | А    |

| D <sub>MAX</sub>         | Maximum duty cycle                                                                                |                                                             |       | 97    |       | %    |

| ISET SETTI               | NG                                                                                                |                                                             |       |       |       |      |

| VISET                    | ISET pin regulated voltage                                                                        |                                                             | 0.985 | 1     | 1.015 | V    |

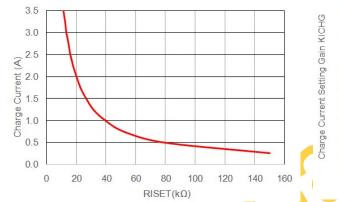

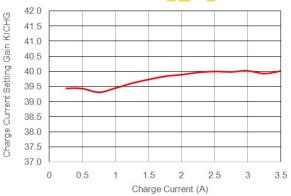

| K <sub>ICHG</sub>        | Charge current setting ratio                                                                      | I <sub>CHG</sub> (A) =<br>K <sub>ICHG</sub> / RISET(kΩ)     |       | 40    | -     | AxkΩ |

| COLD/HOT                 | THERMISTOR COMPARATOR                                                                             |                                                             |       |       |       |      |

| V <sub>T1</sub> %        | T <sub>COLD</sub> (0°C) threshold, charge<br>suspend if V <sub>TS</sub> is above the<br>threshold | $V_{TS}$ rising, as percentage of $V_{REGN}$                |       | 73.5  |       | %    |

| V <sub>T1</sub> %        |                                                                                                   | V <sub>TS</sub> falling, as percentage of V <sub>REGN</sub> |       | 71.5  |       | %    |

| V <sub>T3</sub> %        | T <sub>HOT</sub> (45°C) threshold, charge<br>suspend if V <sub>TS</sub> is below the<br>threshold | V <sub>TS</sub> falling, as percentage of V <sub>REGN</sub> |       | 47.25 |       | %    |

| V <sub>T3</sub> %        |                                                                                                   | V <sub>TS</sub> rising, as percentage of V <sub>REGN</sub>  |       | 48.25 |       | %    |

| THERMAL R                | EGULATION AND THERMAL SHU                                                                         | JTDOWN                                                      |       |       |       |      |

| TREG                     | Thermal regulation                                                                                |                                                             | 110   | 120   | 135   | °C   |

|                          | Thermal shut down                                                                                 | Temperature rise                                            |       | 150   |       | °C   |

| T <sub>SHUT_FALL</sub>   | Thermal shut down                                                                                 | Temperature fall                                            |       | 120   |       | °C   |

| TIMING RE                |                                                                                                   |                                                             |       |       |       |      |

| t <sub>TERM</sub>        | Termination deglitch time                                                                         |                                                             |       | 100   |       | ms   |

| t <sub>SAFETY_FAST</sub> | Fast charge safety timer                                                                          | V <sub>BAT</sub> > V <sub>BAT_LOWV_RISE</sub>               |       | 20    |       | hr   |

| $t_{\text{SAFETY}_PRE}$  | Precharge safety timer                                                                            | V <sub>BAT</sub> < V <sub>BAT_LOWV_RISE</sub>               |       | 2.0   |       | hr   |

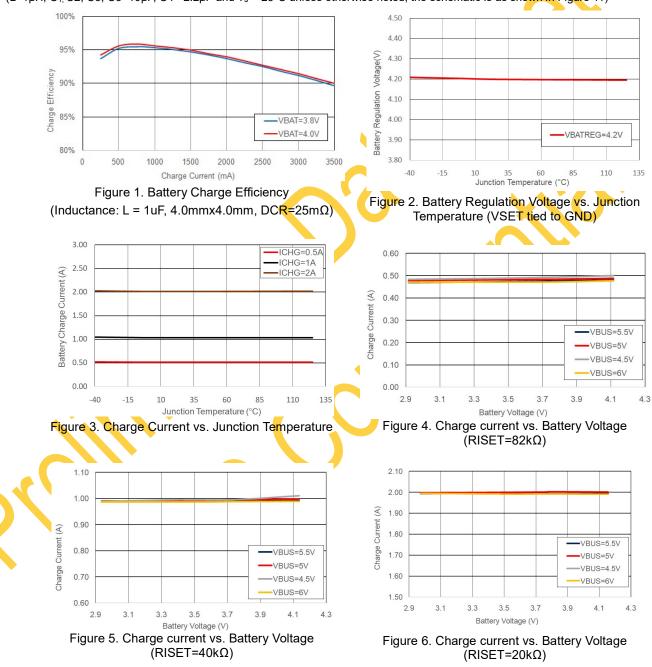

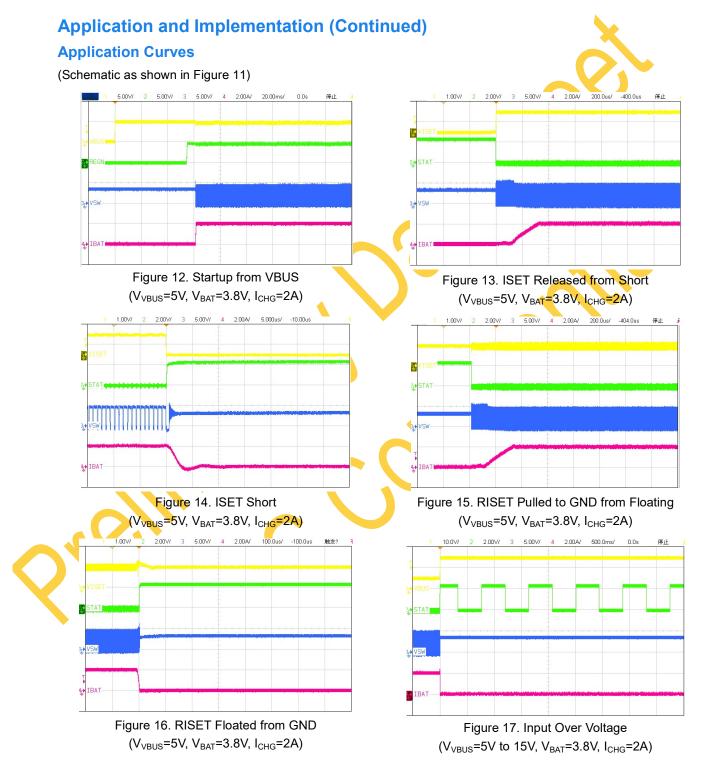

### **Typical Characteristics**

(L=1 $\mu$ H, C<sub>1</sub>, C2, C3, C5=10 $\mu$ F, C4= 2.2 $\mu$ F and T<sub>J</sub> = 25°C unless otherwise noted; the schematic is as shown in Figure 11)

## **Typical Characteristics**

(L1=1 $\mu$ H, C<sub>1</sub>, C2, C3, C5=10 $\mu$ F, C4= 2.2 $\mu$ F and T<sub>J</sub> = 25°C unless otherwise noted; the schematic is as shown in Figure 11)

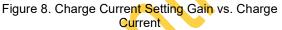

## **Functional Block Diagram**

## **Detailed Description**

#### **Overview**

LP4034

The LP4034 is a highly-integrated switching charger for 1-cell Li-Ion and Li-Polymer batteries. The charge voltage is set by an external resistor connected from VSET pin to GND and the charge current is set by an external resistor connected from ISET pin to GND. The charge current is programmable up to 3.5A. To initiate a charge cycle, the conditions of charger power-up must be met. The device charges battery in four modes: trickle charge, pre-charge, Constant Current (CC) charge, and Constant Voltage (CV) charge. The charger terminates the charge cycle when the charge current is below termination threshold I<sub>TERM</sub> and charge voltage is above recharge threshold. When a fully charged battery's voltage is discharged below recharge threshold, the device automatically starts a new charging cycle and safety timer starts counting. The STAT pin output indicates the charging status of charging, charging complete or charge disabled or charging faults. Charge safety timer is built in to enhance the charger's safety features.

#### **REGN LDO Power-up**

The REGN LDO supplies part of internal bias circuits as well as the HSFET and LSFET gate driver. The REGN also supplies STAT LED indication and internal and external TS resistor dividers. The REGN LDO is enabled after sleep comparator deglitch time, VSET detection time and REGN delay time if the below conditions are met:

- $V_{VBUS}$  above  $V_{VBUS\_LOWV}$

- $V_{VBUS}$  above  $V_{BAT} + V_{SLEEPZ}$

- REGN LDO remains on in fault mode. REGN LDO is powered from VBUS only.

#### Converter and Charger Power-up

Following REGN LDO successful power-up, if there is no below faults detected and ISET pin is normal, converter powers up and charge is enabled. The faults include:

- Input OVP fault: V<sub>VBUS</sub> > V<sub>VBUS</sub>\_ovP

- TS cold/hot fault

- Safety timer fault

- Junction temperature is above T<sub>SHUT</sub>

#### **Device Functional Mode**

The device operates in different modes depending on VBUS voltage, battery voltage and ISET pin connection. The functional modes are listed in the following table.

|                            | I able 1: Device Function                                                                                                                                                                         | nai wode |        |                 |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|-----------------|

| MODE                       | CONDITIONS                                                                                                                                                                                        | REGN     | CHARGE | STAT            |

| ISET Pin Open/Short        | ISET open or short to GND                                                                                                                                                                         | ON       | NO     | OPEN            |

| HiZ Mode                   | V <sub>VBUS</sub> < V <sub>VBUS_LOWV</sub>                                                                                                                                                        | OFF      | NO     | OPEN            |

| Sleep Mode                 | V <sub>VBUS</sub> > V <sub>VBUS_LOWV</sub><br>V <sub>VBUS</sub> < V <sub>BAT+</sub> V <sub>SLEEP Z</sub>                                                                                          | OFF      | NO     | OPEN            |

| Charge Mode                | VVBUS > VVBUS_LOWV<br>VVBUS > VBAT + VSLEEP_Z<br>VVBUS < VVBUS OVP RISE                                                                                                                           | ON       | YES    | SHORT to<br>GND |

| Charge Termination<br>Mode | V <sub>VBUS</sub> > V <sub>VBUS_LOWV</sub><br>V <sub>VBUS</sub> > V <sub>BAT +</sub> V <sub>SLEEP_Z</sub><br>V <sub>VBUS</sub> < V <sub>VBUS_OVP_RISE</sub><br>No faults and charge is terminated | ON       | NO     | OPEN            |

| Fault Mode                 | Any of the faults below if charge mode is<br>initiated:<br>Input OVP<br>TS Cold/Hot<br>Thermal Shutdown<br>Safety timer expires                                                                   | ON       | NO     | BLINKING        |

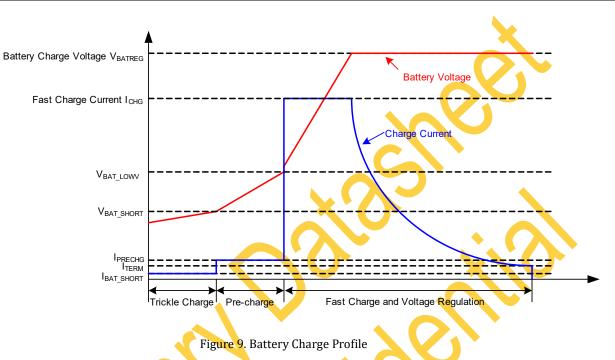

#### Battery Charge Profile

In Charge Mode as shown in the table of Device Functional Mode, the devices charge the battery in four sub-charge-modes: trickle charge, pre-charge, Constant Current (CC) charge and Constant Voltage (CV) charge as shown in Figure 9. If the battery voltage falls below VBAT\_SHORT\_FALL, the battery charge battery with trickle charge current IBAT\_SHORT, when the battery voltage rises above VBAT\_SHORT\_RISE and below VBAT\_LOWV\_RISE, the charger charges battery in precharge mode with charge current at IPRECHG. Fast charge starts once battery voltage rises above VBAT\_LOWV\_RISE. When battery voltage is close to battery charge voltage VBATREG, the charger goes into CV mode and charge current starts to decreases. When charge current decreases below termination current ITERM, charge is terminated and charge cycle ends. Following charge termination, if the battery voltage follows below (VBATREG – VRECHG\_HYS), a new charge cycle restarts.

#### Trickle Charge

The device charges the battery at a fixed charge current  $I_{BAT_SHORT}$  if the battery is below  $V_{BAT} < V_{BAT_SHORT}$ .

#### Precharge

The device charges the battery at 10% of programmed fast charge current  $I_{CHG}$  in precharge mode. Precharge is enabled in charge mode when the precharge condition  $V_{BAT\_SHORT\_RISE} < V_{BAT} < V_{BAT\_LOWV\_RISE}$  are met.

#### **Constant Current (CC) Charge**

CC charge is also called fast charge. The device charges the battery from Buck converter at current level of  $K_{ICHG}$  / RISET, where  $K_{ICHG}$  is the gain of charge current setting. Fast charge starts when fast charge conditions are met.

Table 2. Charge Current in Charge Mode

| CHARGE MODE 🔶  | BATTERY VOLAGE VBAT                | CHARGE CURRENT     | TYPICAL VALUES (mA)       |

|----------------|------------------------------------|--------------------|---------------------------|

| Trickle Charge | VBAT < VBAT_SHORT_FALL             | IBAT_SHORT         | 60                        |

| Precharge      | VBAT_SHORT_RISE < VBAT < VBAT_LOWV | IPRECHG            | 10% of I <sub>CHG</sub>   |

| Fast Charge    | Vbat_lowv < Vbat < Vbatreg         | І <sub>сна</sub>   | K <sub>ICHG</sub> / RISET |

| CV Charge      | Vbat_lowv < Vbat < Vbatreg         | < I <sub>CHG</sub> | Variable                  |

## Constant Voltage (CV) Charge

With the battery voltage charged up, the BAT pin voltage reaches the battery regulation voltage V<sub>BATREG</sub> and the charge current starts to decrease from fast charge current I<sub>CHG</sub>. The actual battery voltage keeps increasing until charge termination is triggered.

### **Charge Termination**

The device terminates a charge cycle when the battery voltage is above recharge threshold ( $V_{BATREG} - V_{RECHG_HYS}$ ) and the charge current is below termination current I<sub>TERM</sub> for deglitch time t<sub>TERM</sub>. The termination current threshold I<sub>TERM</sub> is 10% of fast charge current I<sub>CHG</sub>, which is set by the RISET resistor connected at ISET pin.

### **Battery Recharge**

Once a charge cycle is terminated, safety timer is disabled. If battery voltage  $V_{BAT}$  decreases below the recharge threshold ( $V_{BATREG} - V_{RECHG_HYS}$ ) and the charge mode conditions are met, the charger is enabled again and safety timer is reset and starts counting. Besides recharge, charge cycle could restart if  $V_{VBUS}$  voltage is recycled or ISET pin is released from an open/short/pulled-up condition.

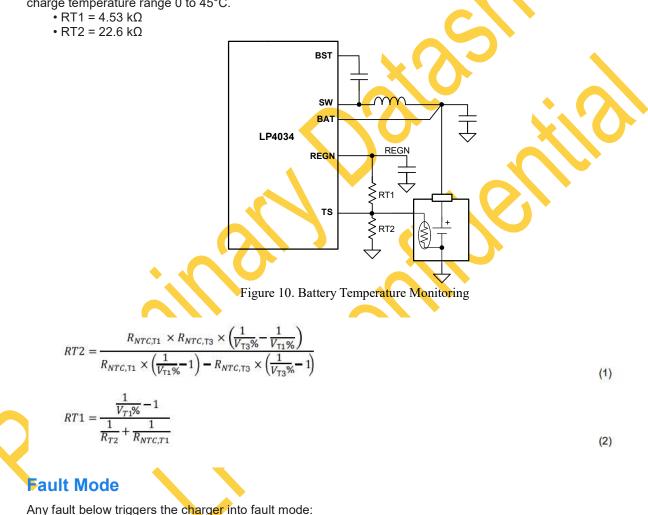

#### **Battery Temperature Monitoring**

The charger device provides a single NTC thermistor input TS pin for battery temperature monitor, RT1 and RT2 resistor programs the cold temperature T1 and hot temperature T3. In the Equations (1) and (2), RNTC T1 is NTC thermistor resistance value at temperature T1 and RNTC,T3 is NTC thermistor resistance values at temperature T3. VT1% and VT3% can be found n the Electronic Characteristics table. Select 0°C to 45°C for battery charge temperature range, then NTC thermistor 103AT-2 resistance are RNTC,T1 = 27.28 k $\Omega$  (at 0°C) and RNTC,T3 = 4.91  $k\Omega$  (at 45°C). From Equation (1) and Equation (2), RT1 and RT2 are derived as below, which is the resistance to set the charge temperature range 0 to 45°C.

- Input OVP 0

- TS Cold/Hot 0

- Thermal Shutdown 0

- Safety timer expiration 0

In fault mode, the charger stops charging and STAT pin blinks. For any faults other than safety timer expiration, the safety timer continues counting until safety timer expires. In fault mode, REGN LDO keeps on and RBFET Q1 is off. Once a fault is cleared, the charger goes back to charge mode if charge conditions are met. The converter goes through soft-start process when going back to charge mode from a fault mode.

#### **ISET Pin Open and Short**

To protect against ISET pin open and short, the charger immediately shuts off once ISET pin is open or short to GND. ISET pin can be used as enable input for charge enable or disable. If ISET pin is pulled higher than 1.3V, charge is disabled as well. When ISET pin is released from open or short or pulled-high, the charger goes through soft-start process.

#### **Charge Safety Timer**

The device has built-in safety timer to prevent extended charging cycle due to abnormal battery conditions. The safety timer is 20 hours when the battery voltage is above VBAT\_LOWV threshold and 2 hours below VBAT\_LOWV threshold. When the safety timer expires, charge is suspended. Safety timer is reset and starts to count each time when charge conditions are met. From the fault mode, one of the following conditions can enable charge and reset safety timer.

- · Battery voltage falls below recharge threshold

- VBUS voltage is recycled

- ISET pin is released from ISET short, open or pulled-high conditions

If the safety timer expires, the charger goes into fault mode and STAT starts blinking. If any faults other than safety timer expiration cause the charger going into fault mode, STAT starts blinking and safety timer continue counting until safety timer expires if a fault stays valid. If a fault is cleared, the charger is out of fault mode and the safety timer continues counting.

#### Input Over Voltage Protection

The device integrates the functionality of an input over-voltage protection (OVP). The input OVP threshold is V<sub>VBUS\_OVP\_RISE</sub>. During an input over-voltage event, the charger is disabled and goes into fault mode.

#### Input Voltage Dynamic Power Management (VINDPM)

When the input current of the device exceeds the current capability of the power supply, the charger device regulates PMID voltage by reducing charge current to avoid crashing the input power supply. VINDPM dynamically tracks the battery voltage. The actual VINDPM regulation is the higher of VINDPM\_MIN and (VBAT + 250mV). To charge a battery, the input voltage must be higher than actual VINDPM threshold.

## Thermal Regulation (TREG)

The device monitors the junction temperature TJ to avoid overheating the chip and limit the device surface temperature. When the internal junction temperature exceeds thermal regulation limit TREG, the device lowers down the charge current. During thermal regulation, the average charging current is usually below the programmed battery charging current. In thermal regulation, termination is temporarily disabled but safety timer continues counting.

## Thermal Shutdown (TSHUT)

The devices have thermal shutdown built in to turn off the charger when device junction temperature exceeds TSHUT. The charger is re-enabled when the junction temperature is 25°C below TSHUT. During thermal shutdown, charge is suspended and the charger goes into fault mode.

### **Application and Implementation**

#### **Application Information**

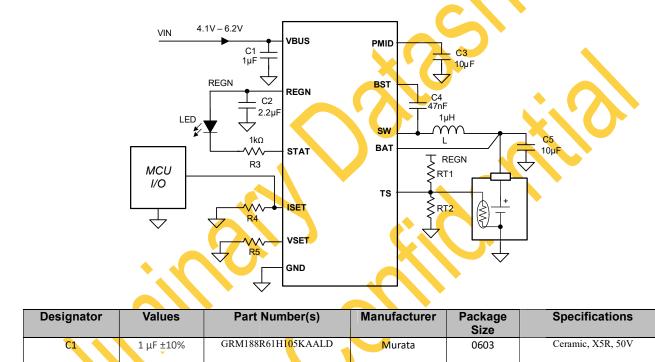

The device can be used for general purpose high efficiency fast charger. The charge voltage can be programmable by a resistor from VSET pin to GND and charge current is programmable by a resistor from ISET pin to GND. The charge can be enabled or disabled by a MCU GPIO port.

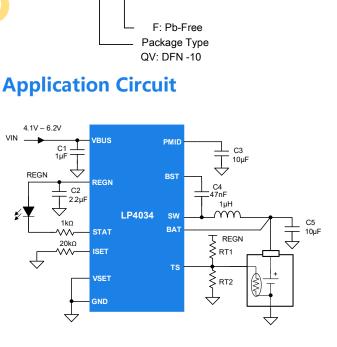

#### **Application Schematic**

|            | C2     | 2.2 μF ±10%           | GRM188R71A225KE15D | Murata    | 0603        | Ceramic, X5R, 10V            |

|------------|--------|-----------------------|--------------------|-----------|-------------|------------------------------|

|            | C3, C5 | $10 \ \mu F \pm 10\%$ | GRM188R61C106KAALD | Murata    | 0603        | Ceramic, X5R, 16V            |

| $\bigcirc$ | L      | 1 μH ±20%             | MPIM252010F1R0M-LF | Microgate | 2.5x2.0x1.0 | Irate=3.2A, DCR= $28m\Omega$ |

| V          | L      | 1 μH ±20%             | FTC404012S1R0MBCA  | SZCJIANG  | 4.0x4.0x1.2 | Irate=5.5A, DCR=21m $\Omega$ |

Figure 11: Typical Applications Schematic

#### **Charge Voltage Setting**

Battery charge voltage is programmed by a resistor connected at the VSET pin. When the REGN LDO startup conditions are met, and before the REGN LDO powers up, the internal VSET detection circuit is enabled to detect VSET pin resistance and set battery charge voltage accordingly. The VSET detection circuit is disabled after detection is complete and changing resistance values on the fly does not change the battery charge voltage for charge safety. VSET detection is re-enabled once the REGN LDO is recycled.

#### **Charge Current Setting**

The charger current is set by the resistor value at the ISET pin according to the equation below:

$I_{CHG}(A) = K_{ICHG}(A \cdot k\Omega) / RISET(k\Omega)$

(3)

$K_{ICHG}$  is current setting gain that is listed in Electrical Characteristics table and RISET is the resistor value from ISET pin to GND.  $K_{ICHG}$  is typically 40 (A·k $\Omega$ ) and the typical values vs. charge currents are illustrated in Figure 8 in Typical Characteristics.

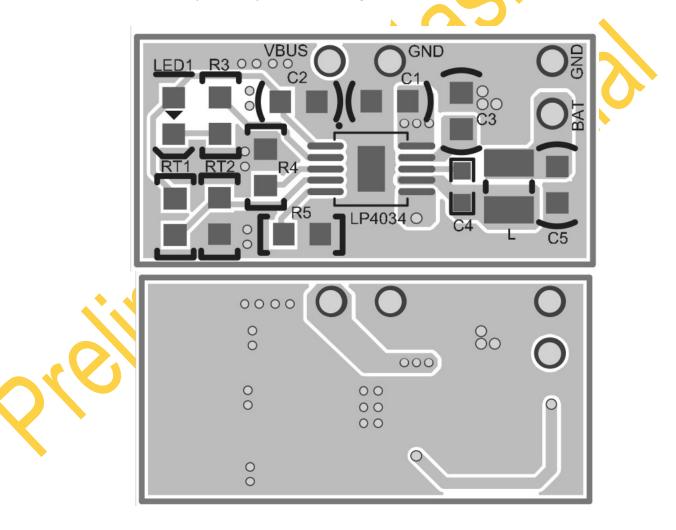

#### **PCB Layout Guideline**

Appropriate PCB layout is important in the power supply design. Good PCB layout minimizes EMI and noises, allows good output voltage regulation and achieves higher efficiency. The following design considerations are recommended:

- Decouple PMID, VBUS and REGN to GND on top layer and place decoupling capacitors as close to those pins

as possible. Always avoid vias if possible because they have parasitic inductance and resistance. If vias are

inevitable, always use more than one vias in parallel to decrease parasitics for power traces.

- Connect GND pad to the ground plane on the bottom side with multiple vias that is for both heat dissipation and electrical connection.

- Minimize switching SW node size and trace lengths and keep it away from ISET and BAT traces.

- An example of a 2-layer PCB layout is shown in Figure 18.

Figure 18. 2-layer PCB Layout Example

| Revision                              | Date         | Change Description                                                                                |

|---------------------------------------|--------------|---------------------------------------------------------------------------------------------------|

| Rev 0.6                               | 12/25/2023   | Initial Release                                                                                   |

|                                       |              |                                                                                                   |

|                                       |              | C                                                                                                 |

|                                       |              |                                                                                                   |

|                                       |              | $\sim \sim $ |

|                                       |              |                                                                                                   |

|                                       | $\sim$       |                                                                                                   |

|                                       |              |                                                                                                   |

|                                       | $\mathbf{O}$ |                                                                                                   |

| · · · · · · · · · · · · · · · · · · · |              |                                                                                                   |

|                                       |              |                                                                                                   |

|                                       |              |                                                                                                   |

|                                       | <b>C</b> \   | J.                                                                                                |

|                                       | C)           |                                                                                                   |

| eill'                                 | $\sim$       |                                                                                                   |

|                                       | S            | <b>J</b> ·                                                                                        |