# 300mA,Ultra-low noise, Small Package Ultra-Fast CMOS LDO Regulator

### **General Description**

The LP3984 is designed for portable RF and wireless applications with demanding performance and space requirements. The LP3984 performance is optimized for battery-powered systems to deliver ultra low noise and low quiescent current. The LP3984 also works with low-ESR ceramic capacitors, reducing the amount of board space necessary for power applications, critical in hand-held wireless devices. The LP3984 consumes less than 1µA in shutdown mode. The other features include ultra low dropout voltage, high output accuracy, current limiting protection, and high ripple rejection ratio. It is available in the 5-lead of SOT23-5 packages.

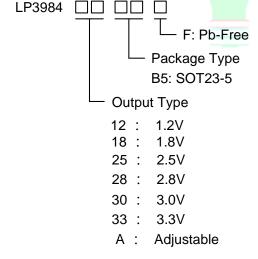

#### **Order Information**

#### **Features**

- Ultra-Low-Noise for RF Application

- ◆ 2.5V- 5.5V Input Voltage Range

- ◆ Low Dropout: 300mV @ 300mA

- 300mA Output Current

- ♦ High PSRR:-70dB at 1KHz

- 1uA Standby Current When Shutdown

- ◆ Available in SOT23-5 Package

- ◆ Ultra-Fast Response in Line/Load transient

- Current Limiting and Thermal Shutdown Protection

### **Applications**

- ♦ Portable Media Players/MP3 player

- Cellular and Smart mobile phone

- ♦ LCD

- ♦ DSC Sensor

- ♦ Wireless Card

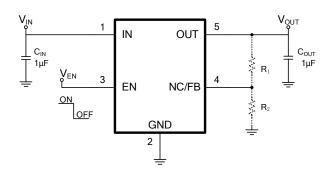

### **Typical Application Circuit**

# **Marking Information**

| Device       | Marking | Package | Shipping |

|--------------|---------|---------|----------|

| LP3984-12B5F | LPS     | SOT23-5 | 3K/REEL  |

|              | 1BYWX   |         |          |

| LP3984-18B5F | LPS     | SOT23-5 | 3K/REEL  |

|              | 1CYWX   |         |          |

| LP3984-25B5F | LPS     | SOT23-5 | 3K/REEL  |

|              | 1DYWX   |         |          |

| LP3984-28B5F | LPS     | SOT23-5 | 3K/REEL  |

|              | 1HYWX   |         |          |

| Device                                                       | Marking | Package | Shipping |  |  |

|--------------------------------------------------------------|---------|---------|----------|--|--|

| LP3984-30B5F                                                 | LPS     | SOT23-5 | 3K/REEL  |  |  |

|                                                              | 1GYWX   |         |          |  |  |

| LP3984-33B5F                                                 | LPS     | SOT23-5 | 3K/REEL  |  |  |

|                                                              | 1EYWX   |         |          |  |  |

| LP3984AB5F                                                   | LPS     | SOT23-5 | 3K/REEL  |  |  |

|                                                              | 1AYWX   |         |          |  |  |

| Marking indication:                                          |         |         |          |  |  |

| Y: Y is year code. W: W is week code. X: X is series number. |         |         |          |  |  |

**Functional Pin Description**

| Package Type | Pin Configurations                                  |  |  |

|--------------|-----------------------------------------------------|--|--|

| SOT-23-5     | Top View SOT23-5  VIN 1 5 VOUT  LPSemi 2  EN 3 4 NC |  |  |

# **Pin Description**

| Pin | Name | Description                                         |  |  |  |

|-----|------|-----------------------------------------------------|--|--|--|

| 1   | VIN  | Power Input Voltage.                                |  |  |  |

| 2   | GND  | Ground.                                             |  |  |  |

| 3   | EN   | Chip Enable (Active High).                          |  |  |  |

| 4   | NC   | No Connection.                                      |  |  |  |

| 4   | FB   | Feedback Pin The Reference Voltage is 0.8V(LP3984A) |  |  |  |

| 5   | VOUT | Output Voltage.                                     |  |  |  |

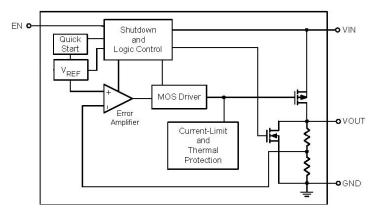

# **Function Diagram**

# **Absolute Maximum Ratings**

| <b></b> | Supply Input Voltage                             | 6.5V                          |

|---------|--------------------------------------------------|-------------------------------|

| <b></b> | Other Pin Voltage                                | 0.3V to V <sub>IN</sub> +0.3V |

| Po      | ower Dissipation, $P_D$ @ $T_A = 25^{\circ}C$    |                               |

| <b></b> | SOT23-5                                          |                               |

| Pa      | Thermal Resistance (SOT23-5) (J <sub>A</sub> )   |                               |

| <b></b> |                                                  |                               |

| <b></b> | Thermal Resistance (SOT23-5) (J <sub>C</sub> )   | 60°C/W                        |

| <b></b> | Maximum Junction Temperature                     | 150℃                          |

| <b></b> | Maximum Soldering Temperature (at leads, 10 sec) | 260℃                          |

| <b></b> | Storage Temperature Range                        | −60°C to 125°C                |

| E       | SD Susceptibility                                |                               |

| <b></b> | HBM (Human Body Mode)                            | 2kV                           |

| <b></b> | MM (Machine-Mode)                                | 200V                          |

| Re      | ecommended Operating Conditions                  |                               |

| <b></b> | Supply Input Voltage                             | 2.5V to 5.5V                  |

| <b></b> | EN Input Voltage                                 | 0V toV <sub>IN</sub> +0.3V    |

| <b></b> | Operation Junction Temperature Range             | −40°C to 125°C                |

| <b></b> | Operation Ambient Temperature Range              | −40°C to 85°C                 |

### **Electrical Characteristics**

( $V_{IN} = V_{OUT} + 1V$ ,  $C_{IN} = C_{OUT} = 1\mu F$ ,  $T_A = 25^{\circ}$  C, unless otherwise specified)

| Para                           | meter                 | Symbol                          | Test Conditions                                               | Min                   | Тур. | Max   | Units                |  |

|--------------------------------|-----------------------|---------------------------------|---------------------------------------------------------------|-----------------------|------|-------|----------------------|--|

| Output Volta                   | ige Accuracy          | $\Delta V_{OUT}$                | I <sub>OUT</sub> =1mA                                         | -2                    |      | +2    | %                    |  |

| Adjustable vol                 | tage reference        | $V_{FB}$                        | LP3984AB5F , IOUT=1mA                                         | 0.784                 | 0.8  | 0.816 | V                    |  |

| Output Load                    | ding Current          | ILOAD                           | V <sub>EN</sub> =V <sub>IN</sub> ,V <sub>IN</sub> >2.8V       | 300                   |      |       | mA                   |  |

| Currer                         | nt Limit              | I <sub>LIM</sub>                | R <sub>LOAD</sub> =1Ω                                         |                       | 500  |       | mA                   |  |

| Quiescer                       | nt Current            | ΙQ                              | V <sub>EN</sub> ≥1.2V, IOUT=0mA                               |                       | 60   | 90    | μΑ                   |  |

|                                |                       |                                 | IOUT=300mA, VOUT=1.2V                                         |                       | 1400 |       | mV                   |  |

|                                | ** *                  | **                              | IOUT=300mA, VOUT=1.8V                                         |                       | 750  |       |                      |  |

| Dropout                        | Voltage               | VDROP                           | IOUT=300mA, VOUT=2.8V                                         |                       | 300  |       |                      |  |

|                                |                       |                                 | IOUT=300mA, VOUT=3.3V                                         |                       | 260  |       |                      |  |

|                                |                       |                                 | $V_{IN}=(V_{OUT}+1V)$ to 5.5V,                                |                       |      | 1     | 0/ <sub>2</sub> /\ / |  |

|                                |                       |                                 | Vout=1.2V,I <sub>OUT</sub> =1mA                               |                       |      | '     | %/V                  |  |

| Lina Pa                        | agulation             | ΔV <sub>LINE</sub>              | $V_{IN}=(V_{OUT}+1V)$ to 5.5V,                                |                       |      | 0.5   | %/V                  |  |

| Line Regulation                |                       | Vout=1.8V,I <sub>OUT</sub> =1mA |                                                               |                       | 0.5  | 70/ V |                      |  |

|                                |                       |                                 | $V_{IN}=(V_{OUT}+1V)$ to 5.5V,<br>$V_{OUT}=3.3V,I_{OUT}=1$ mA | ni                    |      | 0.5   | %/V                  |  |

| Load Re                        | egulation             | ΔL <sub>OAD</sub>               | 1mA <i<sub>OUT&lt;300mA</i<sub>                               | *                     |      | 2     | %/A                  |  |

| Standby                        | Current               | I <sub>STBY</sub>               | V <sub>EN</sub> =GND, Shutdown                                |                       |      | 1     | μA                   |  |

| EN Input B                     | ias Current           | I <sub>BSD</sub>                | V <sub>EN</sub> =3V                                           | V <sub>EN</sub> =3V 1 |      |       | μA                   |  |

| EN Thursday                    | Logic-Low<br>Voltage  | V <sub>IL</sub>                 | V <sub>IN</sub> =3V to 5.5V, Shutdown                         |                       |      | 0.4   | .,                   |  |

| EN Threshold                   | Logic-High<br>Voltage | V <sub>IH</sub>                 | V <sub>IN</sub> =3V to 5.5V, Start-Up                         | 1.2                   |      |       | V                    |  |

| Output No                      | ise Voltage           |                                 | 10Hz to 100kHz, $I_{OUT}$ =200mA, $C_{OUT}$ =1 $\mu$ F        |                       | 300  |       | uVRM<br>S            |  |

| Power Supply<br>Rejection Rate |                       | PSRR                            | $C_{OUT}=2.2\mu F, f=1kHz,$ $I_{OUT}=50mA$                    |                       | -70  |       | dB                   |  |

|                                |                       | I JIKIK                         | $C_{OUT}$ =2.2 $\mu$ F, f = 10 $k$ Hz, $I_{OUT}$ =50 $m$ A    |                       | -60  |       | dB                   |  |

| Thermal Shutdown Temperature   |                       | T <sub>SD</sub>                 |                                                               |                       | 150  |       | $^{\circ}$ C         |  |

### **Applications Information**

Like any low-dropout regulator, the external capacitors used with the LP3984 must be carefully selected for regulator stability and performance. Using a capacitor whose value is > 1µF on the LP3984 input and the amount of capacitance can be increased without limit. The input capacitor must be located a distance of not more than 0.5 inch from the input pin of the IC and returned to a clean analog ground. Any good quality ceramic or tantalum can be used for this capacitor. The capacitor with larger value and lower ESR (equivalent series resistance) provides better PSRR and line-transient response. The output capacitor must meet both requirements for minimum amount of capacitance and ESR in all LDOs application. The LP3984 is designed specifically to work with low ESR ceramic output capacitor in space-saving and performance consideration. Using a ceramic capacitor whose value is at least 1µF with ESR is >  $25m\Omega$  on the LP3984 output ensures stability. The LP3984 still works well with output capacitor of other types due to the wide stable ESR range. Output capacitor of larger capacitance can reduce noise and improve load transient response, stability, and PSRR. The output capacitor should be located not more than 0.5 inch from the VOUT pin of the LP3984 and returned to a clean analog ground.

#### Start-up Function Enable Function

The LP3984 features an LDO regulator enable/disable function. To assure the LDO regulator will switch on, the EN turn on control level must be greater than 1.2 volts. The LDO regulator will go into the shutdown mode when the voltage on the EN pin falls below 0.4 volts. For to protecting the system, the LP3984 have a quick-discharge function. If the enable function is not needed in a specific application, it may be tied to VIN to keep the LDO regulator in a continuously on state.

#### **Set The Output Voltage**

For the adjustable version, the reference voltage of the feedback pin is about 0.8V. The feedback resistance PCB circuit is as small and thick as possible to reduce the interference of some circuits. The resistance of the feedback circuit is selected to be less than  $10M\Omega$ . The output voltage of LDO can be set as follows:

$$V_{OUT} = V_{FB} \times (R_1/R_2 + 1)$$

LP3984-08

Sep.-2023

Email: marketing@lowpowersemi.com

#### **Thermal Considerations**

Thermal protection limits power dissipation in LP3984. When the operation junction temperature exceeds 150  $^{\circ}\mathrm{C}$ , the OTP circuit starts the thermal shutdown function turn the pass element off. The pass element turns on again after the junction temperature cools by 20  $^{\circ}\mathrm{C}$ . For continue operation, do not exceed absolute maximum operation junction temperature 125  $^{\circ}\mathrm{C}$ .

The power dissipation definition in device is:

$$P_D = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{IN} \times I_Q$$

The maximum power dissipation depends on the thermal resistance of IC package, PCB layout, the rate of surroundings airflow and temperature difference between junction to ambient.

The maximum power dissipation can be calculated by following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

Where  $T_{J(MAX)}$  is the maximum operation junction temperature  $125\,^{\circ}\mathrm{C}$ , TA is the ambient temperature and the  $\theta_{JA}$  is the junction to ambient thermal resistance. For recommended operating conditions specification of LP3984, where  $T_{J(MAX)}$  is the maximum junction temperature of the die  $(125\,^{\circ}\mathrm{C})$  and TA is the maximum ambient temperature. The junction to ambient thermal resistance  $(\theta_{JA}$  is layout dependent) for SOT23-5 package is  $195\,^{\circ}\mathrm{C/W}$ .

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / 195 = 500 \text{mW}$$

The maximum power dissipation depends on operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance  $\theta_{JA}$ .

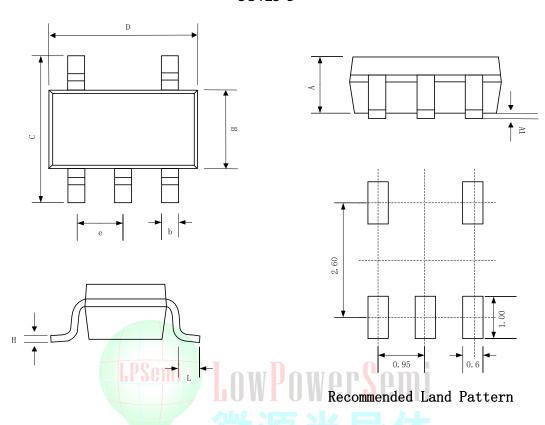

# **Packaging Information**

SOT23-5

| SYMBOL  | Dimensions In Millimeters |       |       |  |  |

|---------|---------------------------|-------|-------|--|--|

| OTWIDGE | MIN                       | NOM   | MAX   |  |  |

| A       | 0.889                     | 1.100 | 1.295 |  |  |

| A1      | 0.000                     | 0.050 | 0.152 |  |  |

| В       | 1.397                     | 1.600 | 1.803 |  |  |

| b       | 0.28                      | 0.35  | 0.559 |  |  |

| С       | 2.591                     | 2.800 | 3.000 |  |  |

| D       | 2.692                     | 2.920 | 3.120 |  |  |

| е       | 0.95BSC                   |       |       |  |  |

| Н       | 0.080                     | 0.152 | 0.254 |  |  |

| L       | 0.300                     | 0.450 | 0.610 |  |  |